|

VAX 4000

The VAX 4000 is a discontinued family of low-end superminicomputers developed and manufactured by Digital Equipment Corporation (later Compaq) using microprocessors implementing the VAX instruction set architecture (ISA). The VAX 4000 succeeded the MicroVAX family, and shipped with the OpenVMS operating system. It was the last family of low-end VAX systems, as the platform was discontinued by Compaq. VAX 4000 Model 300 The VAX 4000 Model 300, code-named "''Pele''", was introduced on 9 July 1990 at DECworld in Boston, Massachusetts, replacing the MicroVAX 3800 and 3900. It used the time-sharing KA670-AA CPU module containing a 35.71 MHz (28 ns cycle time) Rigel chip set with a 128 KB external secondary cache protected by ECC built from 84 ns SRAM. It supported one to four MS670-BA (32 MB) or MS670-CA (64 MB) memory modules for 32 to 256 MB of memory. Q-bus was used for expansion. The Model 300 could be upgraded to a Model 400, Model 500 or Model 600 by ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Superminicomputer

A superminicomputer, colloquially supermini, is a high-end minicomputer. The term is used to distinguish the emerging 32-bit architecture midrange computers introduced in the mid to late 1970s from the classical 16-bit systems that preceded them. The development of these computers was driven by the need of applications to address larger memory. The term midicomputer had been used earlier to refer to these systems. Virtual memory was often an additional criteria that was considered for inclusion in this class of system. The computational speed of these machines was significantly greater than the 16-bit minicomputers and approached the performance of small mainframe computers. The name has at times been described as a "frivolous" term created by "marketeers" that lacks a specific definition. Describing a class of system has historically been seen as problematic: "In the computer kingdom, taxonomic classification of equipment is more of a black art than a science." There is some disa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

L2 Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) whic ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

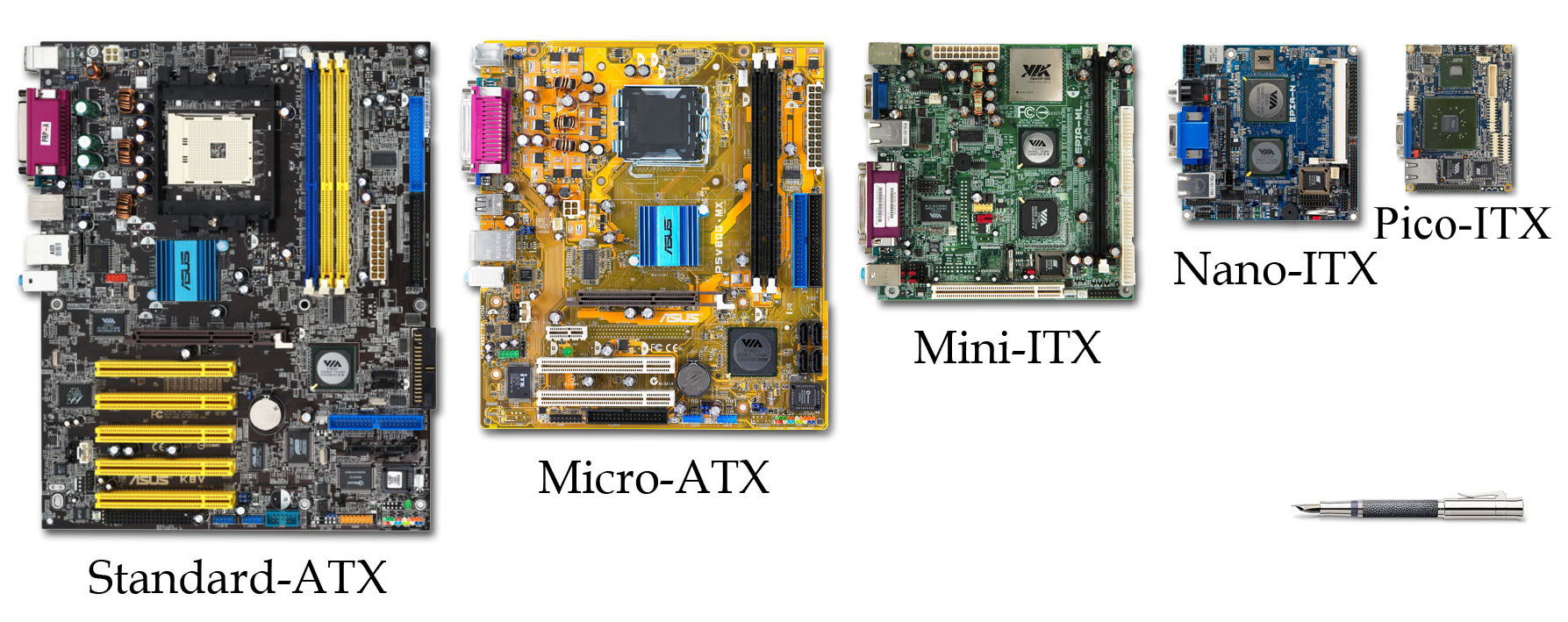

Form Factor (design)

Form factor is a hardware design aspect that defines and prescribes the size, shape, and other physical specifications of components, particularly in electronics. A form factor may represent a broad class of similarly sized components, or it may prescribe a specific standard. It may also define an entire system, as in a computer form factor. Evolution and standardization As electronic hardware has become smaller following Moore's law and related patterns, ever-smaller form factors have become feasible. Specific technological advances, such as PCI Express, have had a significant design impact, though form factors have historically evolved slower than individual components. Standardization of form factors is vital for hardware compatibility between different manufacturers. Trade-offs Smaller form factors may offer more efficient use of limited space, greater flexibility in the placement of components within a larger assembly, reduced use of material, and greater ease of transportat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

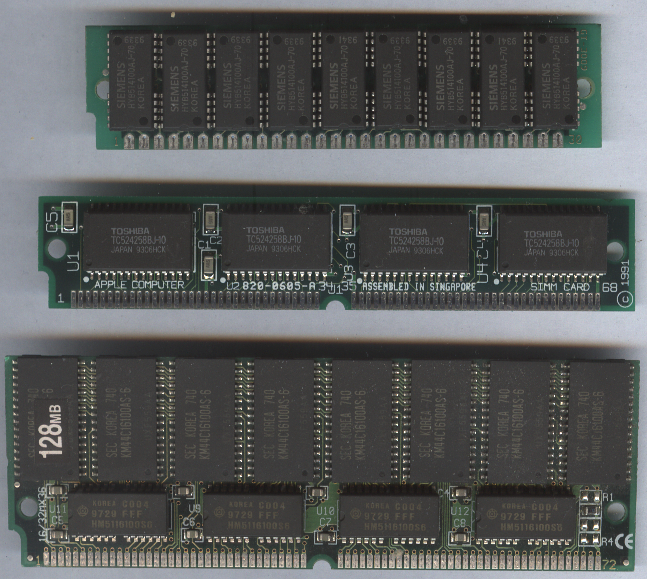

SIMM

A SIMM (single in-line memory module) is a type of memory module used in computers from the early 1980s to the early 2000s. It is a printed circuit board upon which multiple random-access memory Integrated circuit chips are attached to one or both sides. It differs from a dual in-line memory module (DIMM), the most predominant form of memory module since the late 1990s, in that the contacts on a SIMM are redundant on both sides of the module. SIMMs were standardised under the JEDEC JESD-21C standard. Most early PC motherboards ( 8088-based PCs, XTs, and early ATs) used socketed DIP chips for DRAM. As computer memory capacities grew, memory modules were used to save motherboard space and ease memory expansion. Instead of plugging in eight or nine single DIP chips, only one additional memory module was needed to increase the memory of the computer. History SIMMs were invented in 1983 by James E. ClaytonClayton, James E. (1983)Low-cost, high-density memory packaging: A 64K ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Microcode

In processor design, microcode serves as an intermediary layer situated between the central processing unit (CPU) hardware and the programmer-visible instruction set architecture of a computer. It consists of a set of hardware-level instructions that implement the higher-level machine code instructions or control internal finite-state machine sequencing in many digital processing components. While microcode is utilized in Intel and AMD general-purpose CPUs in contemporary desktops and laptops, it functions only as a fallback path for scenarios that the faster hardwired control unit is unable to manage. Housed in special high-speed memory, microcode translates machine instructions, state machine data, or other input into sequences of detailed circuit-level operations. It separates the machine instructions from the underlying electronics, thereby enabling greater flexibility in designing and altering instructions. Moreover, it facilitates the construction of complex multi-step inst ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

L3 Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) whic ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

NVAX

The NVAX is a CMOS microprocessor developed and produced by Digital Equipment Corporation (DEC) that implemented the VAX instruction set architecture (ISA). A variant of the NVAX, the NVAX+, differed in the bus interface and external cache supported, but was otherwise identical in regards to microarchitecture. The NVAX+ was designed to have the same bus as the DECchip 21064, allowing drop-in replacement. The NVAX and NVAX+ was used in late-model VAX systems released in 1991 such as the MicroVAX 3100, VAXstation 4000, VAX 4000, VAX 6000, VAX 7000/10000 and VAXft. Although Digital updated the design throughout the early 1990s, the processors, and the VAX platform itself, were ultimately superseded by the introduction of the DECchip 21064, an implementation of the Alpha (then Alpha AXP) architecture, and the resulting systems in November 1992. The NVAX was offered at a variety of clock speeds, 83.3 MHz (12 ns), 71 MHz (14 ns) and 62.5 MHz (16 ns), while the NVAX+ is clocked ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CVAX

The CVAX is a microprocessor chipset developed and fabricated by Digital Equipment Corporation (DEC) that implemented the VAX instruction set architecture (ISA). The chipset consisted of the CVAX 78034 CPU, CFPA floating-point accelerator, CVAX clock chip, and the associated support chips, the CVAX System Support Chip (CSSC), CVAX Memory Controller (CMCTL), and CVAX Q-Bus Interface Chip (CQBIC). CVAX 78034 The CVAX 78034, also known as the MicroVAX 78034, is a second-generation single-chip VAX microprocessor. Systems featuring the CVAX chip set became available in late 1987. It is clocked at frequencies of 12.5 MHz (80 ns) in higher-end systems such as the VAX 6000 Model 200 and at 11.11 MHz (90 ns) in lower-end systems such as the MicroVAX 3500 and 3600. The 78034 was the first VAX microprocessor to have internal caches, a 1 KB combined instruction and data stream cache. The cache is quite unusual as it is implemented with one-transistor DRAM, whereas the majority ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Backplane

A backplane or backplane system is a group of electrical connectors in parallel with each other, so that each pin of each connector is linked to the same relative pin of all the other connectors, forming a computer bus. It is used to connect several printed circuit boards together to make up a complete computer system. Backplanes commonly use a printed circuit board, but wire-wrapped backplanes have also been used in minicomputers and high-reliability applications. A backplane is generally differentiated from a motherboard by the lack of on-board processing and storage elements. A backplane uses plug-in cards for storage and processing. Usage Early microcomputer systems like the Altair 8800 used a backplane for the processor and expansion cards. Backplanes are normally used in preference to cables because of their greater reliability. In a cabled system, the cables need to be flexed every time that a card is added or removed from the system; this flexing eventually cause ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Q-bus

The Q-bus, also known as the LSI-11 Bus, is one of several bus (computing), bus technologies used with Programmed Data Processor, PDP and VAX, MicroVAX computer systems previously manufactured by the Digital Equipment Corporation of Maynard, Massachusetts, Maynard, Massachusetts. The Q-bus is a less expensive version of Unibus using multiplexing so that address and data signals share the same wires. This allows both a physically smaller and less-expensive implementation of essentially the same functionality. Over time, the physical address range of the Q-bus was expanded from 16 to 18 and then 22 bits. Block transfer modes were also added to the Q-bus. Main features of the Q-bus The Q-bus is arranged as a series of Expansion card, modules installed in one or more Backplane, backplanes. Like the Unibus before it, the Q-bus uses: * ''Memory-mapped I/O'' * ''Byte addressing'' * A strict ''Master-slave (computers), master-slave'' relationship between devices on the bus * ''Asynchro ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Static Random-access Memory

Static random-access memory (static RAM or SRAM) is a type of random-access memory (RAM) that uses latching circuitry (flip-flop) to store each bit. SRAM is volatile memory; data is lost when power is removed. The ''static'' qualifier differentiates SRAM from ''dynamic'' random-access memory (DRAM): * SRAM will hold its data permanently in the presence of power, while data in DRAM decays in seconds and thus must be periodically refreshed. * SRAM is faster than DRAM but it is more expensive in terms of silicon area and cost. * Typically, SRAM is used for the cache and internal registers of a CPU while DRAM is used for a computer's main memory. History Semiconductor bipolar SRAM was invented in 1963 by Robert Norman at Fairchild Semiconductor. Metal–oxide–semiconductor SRAM (MOS-SRAM) was invented in 1964 by John Schmidt at Fairchild Semiconductor. The first device was a 64-bit MOS p-channel SRAM. SRAM was the main driver behind any new CMOS-based technology fab ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ECC Memory

Error correction code memory (ECC memory) is a type of computer data storage that uses an error correction code (ECC) to detect and correct ''n''-bit data corruption which occurs in memory. Typically, ECC memory maintains a memory system immune to single-bit errors: the data that is read from each word is always the same as the data that had been written to it, even if one of the bits actually stored has been flipped to the wrong state. Most non-ECC memory cannot detect errors, although some non-ECC memory with parity support allows detection but not correction. ECC memory is used in most computers where data corruption cannot be tolerated, like industrial control applications, critical databases, and infrastructural memory caches. Concept Error correction codes protect against undetected data corruption and are used in computers where such corruption is unacceptable, examples being scientific and financial computing applications, or in database and file servers. ECC can a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |