|

I5 6400

The following is a list of Intel Core processors. This includes Intel's original Core (Solo/Duo) mobile series based on the Enhanced Pentium M microarchitecture, as well as its Core 2- (Solo/Duo/Quad/Extreme), Core i3-, Core i5-, Core i7-, Core i9-, Core M- (m3/m5/m7/m9), Core 3-, Core 5-, and Core 7- Core 9-, branded processors. Desktop processors Core 2 "Allendale" (65 nm, 800 MT/s) *All models support: '' MMX, SSE, SSE2, SSE3, SSSE3, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementation), Intel Active Management Technology (iAMT2)'' * Die size: 111 mm2 * Steppings: L2, M0, G0 Note: The M0 and G0 Steppings have better optimizations to lower idle power consumption from 12W to 8W. Note: The E4700 uses G0 Stepping which makes it a Conroe CPU. "Conroe" (65 nm, 1066 MT/s) *All models support: '' MMX, SSE, SSE2, SSE3, SSSE3, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementati ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Core 2023 Logo

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California, and Delaware General Corporation Law, incorporated in Delaware. Intel designs, manufactures, and sells computer components such as central processing units (CPUs) and related products for business and consumer markets. It is one of the world's List of largest semiconductor chip manufacturers, largest semiconductor chip manufacturers by revenue, and ranked in the Fortune 500, ''Fortune'' 500 list of the List of largest companies in the United States by revenue, largest United States corporations by revenue for nearly a decade, from 2007 to 2016 Fiscal year, fiscal years, until it was removed from the ranking in 2018. In 2020, it was reinstated and ranked 45th, being the List of Fortune 500 computer software and information companies, 7th-largest technology company in the ranking. It was one of the first companies listed on Nasdaq. Intel supplies List of I ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Core I (15th Gen)

Intel Core is a line of multi-core (with the exception of Core Solo and Core 2 Solo) central processing units (CPUs) for midrange, embedded, workstation, high-end and enthusiast computer markets marketed by Intel Corporation. These processors displaced the existing mid- to high-end Pentium processors at the time of their introduction, moving the Pentium to the entry level. Identical or more capable versions of Core processors are also sold as Xeon processors for the server and workstation markets. Core was launched in January 2006 as a mobile-only series, consisting of single- and dual-core models. It was then succeeded later in July by the Core 2 series, which included both desktop and mobile processors with up to four cores, and introduced 64-bit support. Since 2008, Intel began introducing the Core i3, Core i5, Core i7 and Core i9 lineup of processors, succeeding Core 2. A new naming scheme debuted in 2023, consisting of Core 3, Core 5, and Core 7 for mainstream processo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

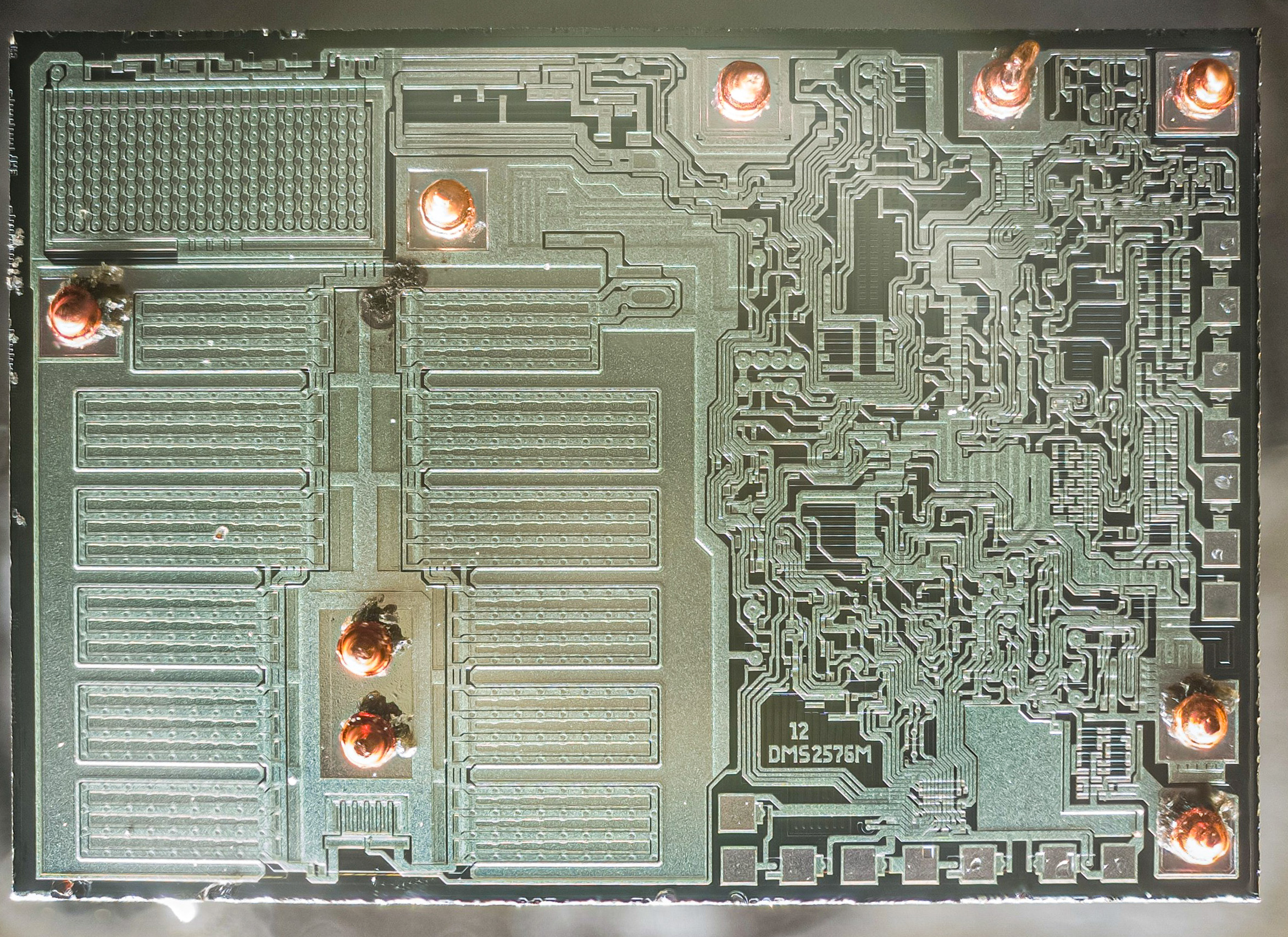

Die (integrated Circuit)

A die, in the context of integrated circuits, is a small block of semiconducting material on which a given functional circuit is Semiconductor fabrication, fabricated. Typically, integrated circuits are produced in large batches on a single wafer (electronics), wafer of electronic-grade Monocrystalline silicon, silicon (EGS) or other semiconductor (such as Gallium arsenide, GaAs) through processes such as photolithography. The wafer is cut (wafer dicing, diced) into many pieces, each containing one copy of the circuit. Each of these pieces is called a die. There are three commonly used plural forms: ''dice'', ''dies,'' and ''die''. To simplify handling and integration onto a printed circuit board, most dies are integrated circuit packaging, packaged in List of electronic component packaging types, various forms. Manufacturing process Most dies are composed of silicon and used for integrated circuits. The process begins with the production of Single crystal, monocrystalline sili ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Active Management Technology

Intel Active Management Technology (AMT) is hardware and firmware for remote out-of-band management of select business computers, running on the Intel Management Engine, a microprocessor subsystem not exposed to the user, intended for monitoring, maintenance, updating, and repairing systems. Out-of-band (OOB) or hardware-based management is different from software-based (or in-band) management and software management agents. Hardware-based management works at a different level from software applications and uses a communication channel (through the TCP/IP stack) that is different from software-based communication (which is through the software stack in the operating system). Hardware-based management does not depend on the presence of an OS or a locally installed management agent. Hardware-based management has been available on Intel/AMD-based computers in the past, but it has largely been limited to auto-configuration using DHCP or BOOTP for dynamic IP address allocation a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

NX Bit

The NX bit (no-execute bit) is a processor feature that separates areas of a virtual address space (the memory layout a program uses) into sections for storing data or program instructions. An operating system supporting the NX bit can mark certain areas of the virtual address space as non-executable, preventing the processor from running any code stored there. This technique, known as executable space protection or Write XOR Execute, protects computers from malicious software that attempts to insert harmful code into another program’s data storage area and execute it, such as in a buffer overflow attack. The term "NX bit" was introduced by Advanced Micro Devices (AMD) as a marketing term. Intel markets this feature as the XD bit (execute disable), while the MIPS architecture refers to it as the XI bit (execute inhibit). In the ARM architecture, introduced in ARMv6, it is known as XN (execute never). The term NX bit is often used broadly to describe similar executable space p ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel 64

x86-64 (also known as x64, x86_64, AMD64, and Intel 64) is a 64-bit extension of the x86 instruction set. It was announced in 1999 and first available in the AMD Opteron family in 2003. It introduces two new operating modes: 64-bit mode and compatibility mode, along with a new four-level paging mechanism. In 64-bit mode, x86-64 supports significantly larger amounts of virtual memory and physical memory compared to its 32-bit predecessors, allowing programs to utilize more memory for data storage. The architecture expands the number of general-purpose registers from 8 to 16, all fully general-purpose, and extends their width to 64 bits. Floating-point arithmetic is supported through mandatory SSE2 instructions in 64-bit mode. While the older x87 FPU and MMX registers are still available, they are generally superseded by a set of sixteen 128-bit vector registers (XMM registers). Each of these vector registers can store one or two double-precision floating-point numbers, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SpeedStep

Enhanced SpeedStep is a series of dynamic frequency scaling technologies (codenamed Geyserville and including SpeedStep, SpeedStep II, and SpeedStep III) built into some Intel's microprocessors that allow the clock speed of the processor to be dynamically changed (to different ''P-states'') by software. This allows the processor to meet the instantaneous performance needs of the operation being performed, while minimizing power draw and heat generation. EIST (SpeedStep III) was introduced in several Prescott 6 series in the first quarter of 2005, namely the Pentium 4 660. Intel Speed Shift Technology (SST) was introduced in Intel Skylake Processor. Enhanced Intel SpeedStep Technology is sometimes abbreviated as EIST. Intel's trademark of "Intel SpeedStep" was canceled due to the trademark being invalidated in 2012. Explanation Running a processor at high clock speeds allows for better performance. However, when the same processor is run at a lower frequency (speed), it gene ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSSE3

Supplemental Streaming SIMD Extensions 3 (SSSE3 or SSE3S) is a SIMD instruction set created by Intel and is the fourth iteration of the SSE technology. History SSSE3 was first introduced with Intel processors based on the Core microarchitecture on June 26, 2006 with the "Woodcrest" Xeons. SSSE3 has been referred to by the codenames Tejas New Instructions (TNI) or Merom New Instructions (MNI) for the first processor designs intended to support it. SSSE3 has enhanced for HD audio/video decoding/encoding, for example AAC. Functionality SSSE3 contains 16 new discrete instructions. Each instruction can act on 64-bit MMX or 128-bit XMM registers. Therefore, Intel's materials refer to 32 new instructions. They include: * Twelve instructions that perform horizontal addition or subtraction operations. * Six instructions that evaluate absolute values. * Two instructions that perform multiply-and-add operations and speed up the evaluation of dot products. * Two instructions tha ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSE3

SSE3, Streaming SIMD Extensions 3, also known by its Intel code name Prescott New Instructions (PNI), is the third iteration of the SSE instruction set for the IA-32 (x86) architecture. Intel introduced SSE3 in early 2004 with the Prescott revision of their Pentium 4 CPU. In April 2005, AMD introduced a subset of SSE3 in revision E (Venice and San Diego) of their Athlon 64 CPUs. The earlier SIMD instruction sets on the x86 platform, from oldest to newest, are MMX, 3DNow! (developed by AMD, no longer supported on newer CPUs), SSE, and SSE2. SSE3 contains 13 new instructions over SSE2. Changes The most notable change is the capability to work horizontally in a register, as opposed to the more or less strictly vertical operation of all previous SSE instructions. More specifically, instructions to add and subtract the multiple values stored within a single register have been added. These instructions can be used to speed up the implementation of a number of DSP and 3D op ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets introduced by Intel with the initial version of the Pentium 4 in 2000. SSE2 instructions allow the use of XMM (SIMD) registers on x86 instruction set architecture processors. These registers can load up to 128 bits of data and perform instructions, such as vector addition and multiplication, simultaneously. SSE2 introduced double-precision floating point instructions in addition to the single-precision floating point and integer instructions found in SSE. SSE2 extends earlier SSE instruction set by adding 144 new instructions to the previous 70 instructions. SSE2 intends to fully replace MMX, a SIMD instruction set found on IA-32 architecture processors. Competing chip-maker AMD added support for SSE2 with the introduction of their Opteron and Athlon 64 ranges of AMD64 64-bit CPUs in 2003. SSE2 was extended to create SSE3 in 2004, and e ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Streaming SIMD Extensions

In computing, Streaming SIMD Extensions (SSE) is a single instruction, multiple data ( SIMD) instruction set extension to the x86 architecture, designed by Intel and introduced in 1999 in its Pentium III series of central processing units (CPUs) shortly after the appearance of Advanced Micro Devices (AMD's) 3DNow!. SSE contains 70 new instructions (65 unique mnemonics using 70 encodings), most of which work on single precision floating-point data. SIMD instructions can greatly increase performance when exactly the same operations are to be performed on multiple data objects. Typical applications are digital signal processing and graphics processing. Intel's first IA-32 SIMD effort was the MMX instruction set. MMX had two main problems: it re-used existing x87 floating-point registers making the CPUs unable to work on both floating-point and SIMD data at the same time, and it only worked on integers. SSE floating-point instructions operate on a new independent register s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MMX (instruction Set)

MMX is a ''single instruction, multiple data'' (SIMD) instruction set architecture designed by Intel, introduced on January 8, 1997 with its Pentium P5 (microarchitecture) based line of microprocessors, named "Pentium with MMX Technology". It developed out of a similar unit introduced on the Intel i860, and earlier the Intel i750 video pixel processor. MMX is a processor supplementary capability that is supported on IA-32 processors by Intel and other vendors . AMD also added MMX instruction set in its AMD K6, K6 processor. ''The New York Times'' described the initial push, including Super Bowl advertisements, as focused on "a new generation of glitzy multimedia products, including videophones and 3-D video games." MMX has subsequently been extended by several programs by Intel and others: 3DNow!, Streaming SIMD Extensions (SSE), and ongoing revisions of Advanced Vector Extensions (AVX). Overview Naming MMX is officially a meaningless initialism trademarked by Intel; unoffici ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |