|

SPARC T5

SPARC T5 is the fifth generation multicore microprocessor of Oracle's SPARC T series family. It was first presented at Hot Chips 24 in August 2012, and was officially introduced with the Oracle SPARC T5 servers in March 2013. The processor is designed to offer high multithreaded performance (16 cores per chip, with 8 threads per core), as well as high single threaded performance from the same chip. The processor uses the same SPARC S3 core design as its predecessor, the SPARC T4 processor, but is implemented in a 28 nm process and runs at 3.6 GHz. The S3 core is a dual-issue core that uses dynamic threading and out-of-order execution, incorporates one floating point unit, one dedicated cryptographic unit per core. The 64-bit SPARC Version 9 based processor has 16 cores supporting up to 128 threads per processor, and scales up to 1,024 threads in an 8 socket system. Other changes include the support of PCIe version 3.0 and a new cache coherence protocol. SPARC ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SPARC V9

SPARC (Scalable Processor Architecture) is a reduced instruction set computer (RISC) instruction set architecture originally developed by Sun Microsystems. Its design was strongly influenced by the experimental Berkeley RISC system developed in the early 1980s. First developed in 1986 and released in 1987, SPARC was one of the most successful early commercial RISC systems, and its success led to the introduction of similar RISC designs from many vendors through the 1980s and 1990s. The first implementation of the original 32-bit architecture (SPARC V7) was used in Sun's Sun-4 computer workstation and server systems, replacing their earlier Sun-3 systems based on the Motorola 68000 series of processors. SPARC V8 added a number of improvements that were part of the SuperSPARC series of processors released in 1992. SPARC V9, released in 1993, introduced a 64-bit architecture and was first released in Sun's UltraSPARC processors in 1995. Later, SPARC processors were used in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CPU Socket

In computer hardware, a CPU socket or CPU slot contains one or more mechanical components providing mechanical and electrical connections between a microprocessor and a printed circuit board (PCB). This allows for placing and replacing the central processing unit (CPU) without soldering. Common sockets have retention clips that apply a constant force, which must be overcome when a device is inserted. For chips with many pins, zero insertion force (ZIF) sockets are preferred. Common sockets include Pin Grid Array (PGA) or Land Grid Array (LGA). These designs apply a compression force once either a handle (PGA type) or a surface plate (LGA type) is put into place. This provides superior mechanical retention while avoiding the risk of bending pins when inserting the chip into the socket. Certain devices use Ball Grid Array (BGA) sockets, although these require soldering and are generally not considered user replaceable. CPU sockets are used on the motherboard in desktop and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Oracle Microprocessors

An oracle is a person or agency considered to provide wise and insightful counsel or prophetic predictions, most notably including precognition of the future, inspired by deities. As such, it is a form of divination. Description The word ''oracle'' comes from the Latin verb ''ōrāre'', "to speak" and properly refers to the priest or priestess uttering the prediction. In extended use, ''oracle'' may also refer to the ''site of the oracle'', and to the oracular utterances themselves, called ''khrēsmē'' 'tresme' (χρησμοί) in Greek. Oracles were thought to be portals through which the gods spoke directly to people. In this sense, they were different from seers (''manteis'', μάντεις) who interpreted signs sent by the gods through bird signs, animal entrails, and other various methods.Flower, Michael Attyah. ''The Seer in Ancient Greece.'' Berkeley: University of California Press, 2008. The most important oracles of Greek antiquity were Pythia (priestess to Apoll ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cache Coherence

In computer architecture, cache coherence is the uniformity of shared resource data that ends up stored in multiple local caches. When clients in a system maintain caches of a common memory resource, problems may arise with incoherent data, which is particularly the case with CPUs in a multiprocessing system. In the illustration on the right, consider both the clients have a cached copy of a particular memory block from a previous read. Suppose the client on the bottom updates/changes that memory block, the client on the top could be left with an invalid cache of memory without any notification of the change. Cache coherence is intended to manage such conflicts by maintaining a coherent view of the data values in multiple caches. Overview In a shared memory multiprocessor system with a separate cache memory for each processor, it is possible to have many copies of shared data: one copy in the main memory and one in the local cache of each processor that requested it. When on ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Glueless

In electronics, glue logic is the custom logic circuitry used to interface a number of off-the-shelf integrated circuits. This is often achieved using common, inexpensive 7400- or 4000-series components. In more complex cases, a programmable logic device like a CPLD or FPGA might be used. The falling price of programmable logic devices, combined with their reduced size and power consumption compared to discrete components, is making them common even for simple systems. In addition, programmable logic can be used to hide the exact function of a circuit, in order to prevent a product from being cloned or counterfeited. The software equivalent of glue logic is called glue code. Usage Typical functions of glue logic may include: * Simple logic functions. * Address decoding circuitry used with older processors like the MOS Technology 6502 or Zilog Z80 to divide up the processor's address space into RAM, ROM and I/O. Newer versions of these processors, such as the WDC 65816 or the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Directory-based Cache Coherence

In computer engineering, directory-based cache coherence is a type of cache coherence mechanism, where directories are used to manage caches in place of bus snooping. Bus snooping methods scale poorly due to the use of broadcasting. These methods can be used to target both performance and scalability of directory systems. Full bit vector format In the full bit vector format, for each possible cache line in memory, a bit is used to track whether every individual processor has that line stored in its cache. The full bit vector format is the simplest structure to implement, but the least scalable. The SGI Origin 2000 uses a combination of full bit vector and coarse bit vector depending on the number of processors. Each directory entry must have 1 bit stored per processor per cache line, along with bits for tracking the state of the directory. This leads to the total size required being ''(number of processors)×number of cache lines'', having a storage overhead ratio of ''(n ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cache Coherence

In computer architecture, cache coherence is the uniformity of shared resource data that ends up stored in multiple local caches. When clients in a system maintain caches of a common memory resource, problems may arise with incoherent data, which is particularly the case with CPUs in a multiprocessing system. In the illustration on the right, consider both the clients have a cached copy of a particular memory block from a previous read. Suppose the client on the bottom updates/changes that memory block, the client on the top could be left with an invalid cache of memory without any notification of the change. Cache coherence is intended to manage such conflicts by maintaining a coherent view of the data values in multiple caches. Overview In a shared memory multiprocessor system with a separate cache memory for each processor, it is possible to have many copies of shared data: one copy in the main memory and one in the local cache of each processor that requested it. When on ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

International Data Corporation

International Data Group (IDG, Inc.) is a market intelligence and demand generation company focused on the technology industry. IDG, Inc.’s mission is centered around supporting the technology industry through research, data, marketing technology, and insights that help create and sustain relationships between businesses. IDG, Inc. is wholly owned by Blackstone and is led by Mohamad Ali, who was appointed CEO of the company in 2019. Ali serves on IDG, Inc.’s leadership team along with IDC President Crawford Del Prete, IDG, Inc.’s Chief Financial Officer Donna Marr, and Foundry President Kumaran Ramanathan. IDG, Inc. is headquartered in Needham, MA and is parent company to both International Data Corporation (IDC) and Foundry (formerly IDG Communications). History International Data Group was initially founded as International Data Corporate (IDC) in 1964 by Patrick Joseph McGovern, shortly after he had graduated from the Massachusetts Institute of Technology (MIT). Ba ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SPARC T-Series

The SPARC T-series family of RISC processors and server computers, based on the SPARC V9 architecture, was originally developed by Sun Microsystems, and later by Oracle Corporation after its acquisition of Sun. Its distinguishing feature from earlier SPARC iterations is the introduction of chip multithreading (CMT) technology, a multithreading, multicore design intended to drive greater processor utilization at lower power consumption. The first generation T-series processor, the UltraSPARC T1, and servers based on it, were announced in December 2005. As later generations were introduced, the term "T series" was used to refer to the entire family of processors. Pre-Oracle era Sun Microsystems' Sun Fire and SPARC Enterprise product lines were based on early generations of CMT technology. The UltraSPARC T1 based Sun Fire T2000 and T1000 servers were launched in December 2005 and early 2006, respectively. They were later rebranded to match the name of the UltraSPARC T2 and T2 Plus b ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Power Management

Power management is a feature of some electrical appliances, especially copiers, computers, computer CPUs, computer GPUs and computer peripherals such as monitors and printers, that turns off the power or switches the system to a low-power state when inactive. In computing this is known as PC power management and is built around a standard called ACPI, this supersedes APM. All recent computers have ACPI support. Motivations PC power management for computer systems is desired for many reasons, particularly: * Reduce overall energy consumption * Prolong battery life for portable and embedded systems * Reduce cooling requirements * Reduce noise * Reduce operating costs for energy and cooling Lower power consumption also means lower heat dissipation, which increases system stability, and less energy use, which saves money and reduces the impact on the environment. Processor level techniques The power management for microprocessors can be done over the whole processor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

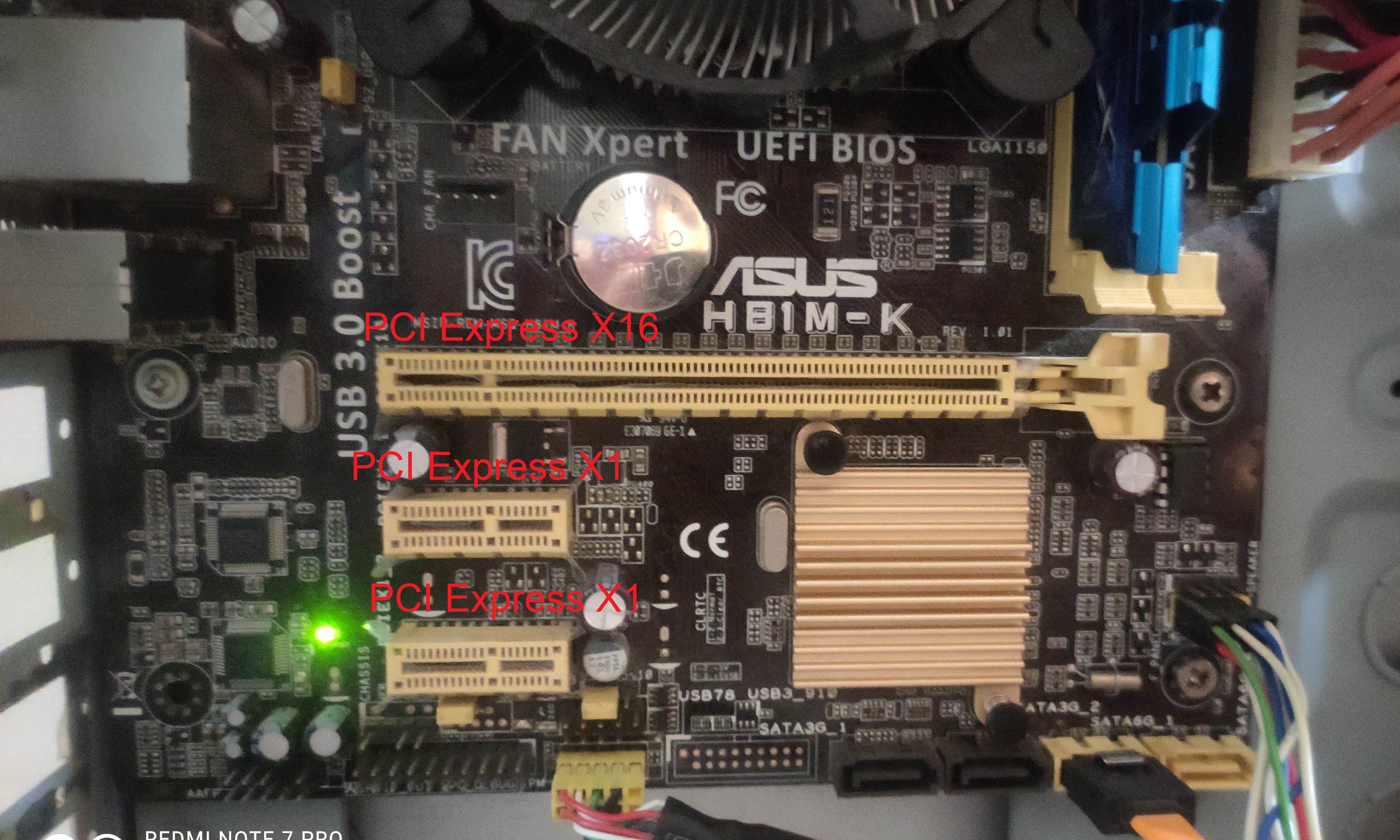

PCIE

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both directi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Die (integrated Circuit)

A die, in the context of integrated circuits, is a small block of semiconducting material on which a given functional circuit is fabricated. Typically, integrated circuits are produced in large batches on a single wafer of electronic-grade silicon (EGS) or other semiconductor (such as GaAs) through processes such as photolithography. The wafer is cut ( diced) into many pieces, each containing one copy of the circuit. Each of these pieces is called a die. There are three commonly used plural forms: ''dice'', ''dies'' and ''die''. To simplify handling and integration onto a printed circuit board, most dies are packaged in various forms. Manufacturing process Most dies are composed of silicon and used for integrated circuits. The process begins with the production of monocrystalline silicon ingots. These ingots are then sliced into disks with a diameter of up to 300 mm. [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |