|

Lion Cove

Lion Cove is a 64-bit x86 CPU core architecture designed by Intel. The Lion Cove core is featured in Core Ultra Series 2 Arrow Lake and Lunar Lake processors. Architecture Lion Cove is a performance core architecture aimed at providing high computing performance with wider integer and vector execution units, wider fetch and increased core frequencies compared to the Intel's density-optimized E-core architectures. Intel claims a 14% increase in instructions per cycle (IPC) with the Lion Cove P-core over Redwood Cove. Intel approached the Lion Cove design process with the intention to "remove any transistor from the design that doesn't directly contribute to productivity", stripping down the core design in order to focus on single-threading and core area efficiency. Ori Lempel served as Senior Principal Engineer for the Lion Cove- P-core design. Front end The front-end of the Lion Cove core for fetching, decoding and issuing instructions has been made wider and deeper. There is ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California, and Delaware General Corporation Law, incorporated in Delaware. Intel designs, manufactures, and sells computer components such as central processing units (CPUs) and related products for business and consumer markets. It is one of the world's List of largest semiconductor chip manufacturers, largest semiconductor chip manufacturers by revenue, and ranked in the Fortune 500, ''Fortune'' 500 list of the List of largest companies in the United States by revenue, largest United States corporations by revenue for nearly a decade, from 2007 to 2016 Fiscal year, fiscal years, until it was removed from the ranking in 2018. In 2020, it was reinstated and ranked 45th, being the List of Fortune 500 computer software and information companies, 7th-largest technology company in the ranking. It was one of the first companies listed on Nasdaq. Intel supplies List of I ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AVX-512

AVX-512 are 512-bit extensions to the 256-bit Advanced Vector Extensions SIMD instructions for x86 instruction set architecture (ISA) proposed by Intel in July 2013, and first implemented in the 2016 Intel Xeon Phi x200 (Knights Landing), and then later in a number of AMD and other Intel CPUs ( see list below). AVX-512 consists of multiple extensions that may be implemented independently. This policy is a departure from the historical requirement of implementing the entire instruction block. Only the core extension AVX-512F (AVX-512 Foundation) is required by all AVX-512 implementations. Besides widening most 256-bit instructions, the extensions introduce various new operations, such as new data conversions, scatter operations, and permutations. The number of AVX registers is increased from 16 to 32, and eight new "mask registers" are added, which allow for variable selection and blending of the results of instructions. In CPUs with the vector length (VL) extension—included in m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Redwood Cove

Sequoioideae, commonly referred to as redwoods, is a subfamily of coniferous trees within the family Cupressaceae, that range in the northern hemisphere. It includes the largest and tallest trees in the world. The trees in the subfamily are amongst the most notable trees in the world and are common ornamental trees. The subfamily reached its peak of diversity during the early Cenozoic. Description The three redwood subfamily genera are '' Sequoia'' from coastal California and Oregon, ''Sequoiadendron'' from California's Sierra Nevada, and ''Metasequoia'' in China. The redwood subfamily contains the largest and tallest trees in the world. These trees can live for thousands of years. Threats include logging, fire suppression, and burl poaching. Only two of the genera, ''Sequoia'' and ''Sequoiadendron'', are known for massive trees. Trees of ''Metasequoia'', from the single living species ''Metasequoia glyptostroboides'', are deciduous, grow much smaller (although are still large ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Golden Cove

Golden Cove is a codename for a CPU microarchitecture developed by Intel and released in November 2021. It succeeds four microarchitectures: Sunny Cove, Skylake, Willow Cove, and Cypress Cove. It is fabricated using Intel's Intel 7 process node, previously referred to as 10nm Enhanced SuperFin (10ESF). The microarchitecture is used in the high-performance cores (P-core) of the 12th-generation Intel Core processors (codenamed " Alder Lake") and fourth-generation Xeon Scalable server processors (codenamed "Sapphire Rapids"). History and features Intel first unveiled Golden Cove during their Architecture Day 2020, with further details released at the same event in August 2021. Similar to Skylake, Golden Cove was described by Intel as a major update to the core microarchitecture, with Intel stating that it would "allow performance for the next decade of compute". Intel also described Golden Cove as the largest microarchitectural upgrade to the Core family in a decade, toutin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Skylake (microarchitecture)

Skylake is Intel's codename for its sixth generation Core microprocessor family that was launched on August 5, 2015, succeeding the Broadwell microarchitecture. Skylake is a microarchitecture redesign using the same 14 nm manufacturing process technology as its predecessor, serving as a tock in Intel's tick–tock manufacturing and design model. According to Intel, the redesign brings greater CPU and GPU performance and reduced power consumption. Skylake CPUs share their microarchitecture with Kaby Lake, Coffee Lake, Whiskey Lake, and Comet Lake CPUs. Skylake is the last Intel platform on which Windows earlier than Windows 10 are officially supported by Microsoft, although enthusiast-created modifications are available that disabled the Windows Update check and allowed Windows 8.1 and earlier to continue to receive Windows Updates on this and later platforms. Some of the processors based on the Skylake microarchitecture are marketed as sixth-generation Core. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Pentium 4

Pentium 4 is a series of single-core central processing unit, CPUs for Desktop computer, desktops, laptops and entry-level Server (computing), servers manufactured by Intel. The processors were shipped from November 20, 2000 until August 8, 2008. All Pentium 4 CPUs are based on the NetBurst microarchitecture, the successor to the P6 (microarchitecture), P6. The Pentium 4 #Willamette, Willamette (180 nm) introduced SSE2, while the #Prescott, Prescott (90 nm) introduced SSE3 and later 64-bit technology. Later versions introduced Hyper-threading, Hyper-Threading Technology (HTT). The first Pentium 4-branded processor to implement x86-64, 64-bit was the Prescott (90 nm) (February 2004), but this feature was not enabled. Intel subsequently began selling 64-bit Pentium 4s using the ''"E0" revision'' of the Prescotts, being sold on the OEM market as the Pentium 4, model F. The E0 revision also adds eXecute Disable (XD) (Intel's name for the NX bit) to Intel 64. Int ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Die (integrated Circuit)

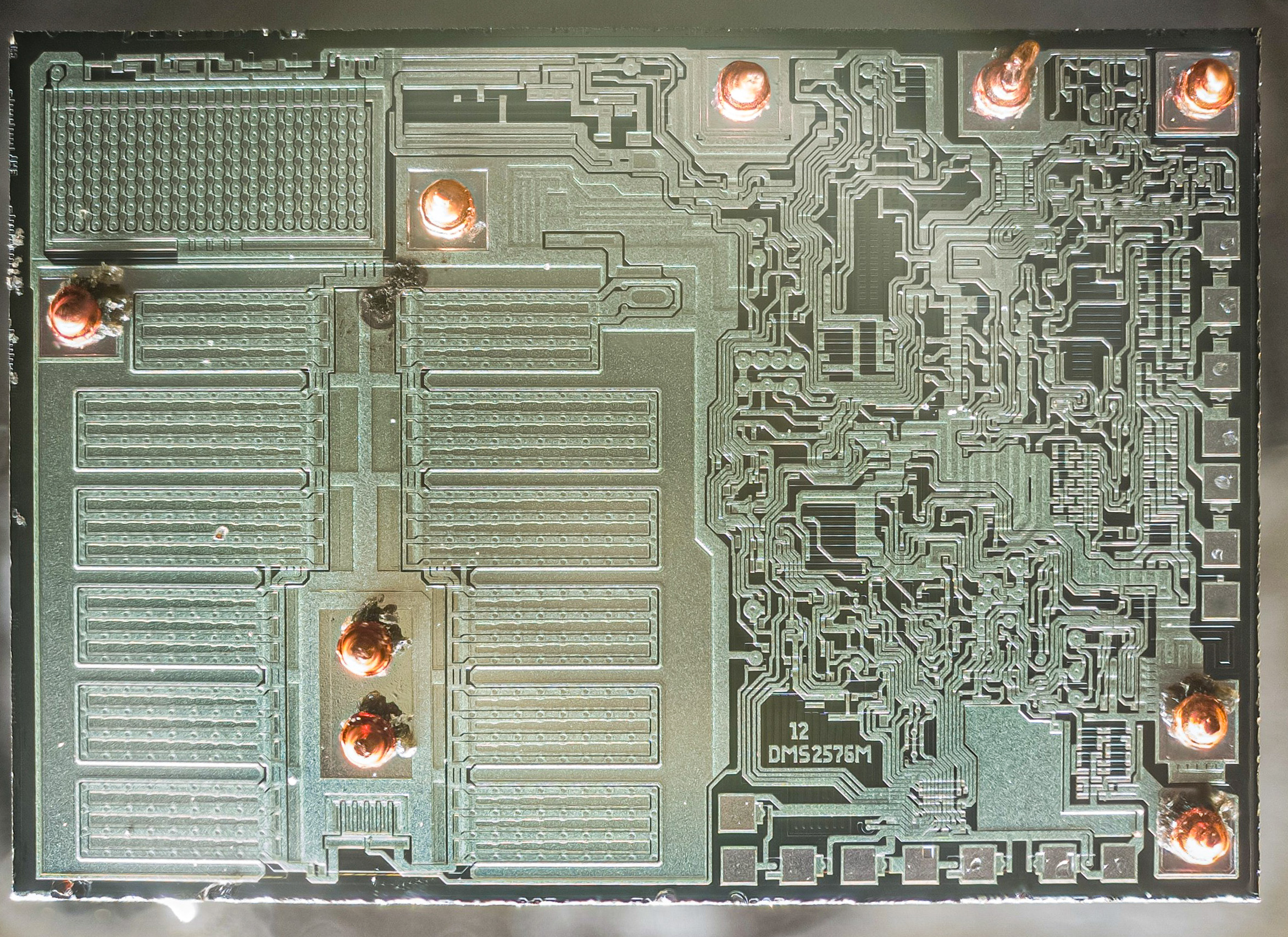

A die, in the context of integrated circuits, is a small block of semiconducting material on which a given functional circuit is Semiconductor fabrication, fabricated. Typically, integrated circuits are produced in large batches on a single wafer (electronics), wafer of electronic-grade Monocrystalline silicon, silicon (EGS) or other semiconductor (such as Gallium arsenide, GaAs) through processes such as photolithography. The wafer is cut (wafer dicing, diced) into many pieces, each containing one copy of the circuit. Each of these pieces is called a die. There are three commonly used plural forms: ''dice'', ''dies,'' and ''die''. To simplify handling and integration onto a printed circuit board, most dies are integrated circuit packaging, packaged in List of electronic component packaging types, various forms. Manufacturing process Most dies are composed of silicon and used for integrated circuits. The process begins with the production of Single crystal, monocrystalline sili ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

EDRAM

Embedded DRAM (eDRAM) is dynamic random-access memory (DRAM) integrated on the same die or multi-chip module (MCM) of an application-specific integrated circuit (ASIC) or microprocessor. eDRAM's cost-per-bit is higher when compared to equivalent standalone DRAM chips used as external memory, but the performance advantages of placing eDRAM onto the same chip as the processor outweigh the cost disadvantages in many applications. In performance and size, eDRAM is positioned between level 3 cache and conventional DRAM on the memory bus, and effectively functions as a level 4 cache, though architectural descriptions may not explicitly refer to it in those terms. Embedding memory on the ASIC or processor allows for much wider buses and higher operation speeds, and due to much higher density of DRAM in comparison to SRAM, larger amounts of memory can be installed on smaller chips if eDRAM is used instead of eSRAM. eDRAM requires additional fab process steps compared with embedded ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Broadwell (microarchitecture)

Broadwell (previously Rockwell) is the fifth generation of the Intel Core processor. It is Intel's codename for the 14 nanometer die shrink of its Haswell microarchitecture. It is a "tick" in Intel's tick–tock principle as the next step in semiconductor fabrication. Like some of the previous tick-tock iterations, Broadwell did not completely replace the full range of CPUs from the previous microarchitecture ( Haswell), as there were no low-end desktop CPUs based on Broadwell. Some of the processors based on the Broadwell microarchitecture are marketed as "5th-generation Core" i3, i5 and i7 processors. This moniker is however not used for marketing of the Broadwell-based Celeron, Pentium or Xeon chips. This microarchitecture also introduced the Core M processor branding. Broadwell's H and C variants are used in conjunction with Intel 9 Series chipsets ( Z97, H97 and HM97), in addition to retaining backward compatibility with some of the Intel 8 Series chipse ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cache Hierarchy

Cache hierarchy, or multi-level cache, is a memory architecture that uses a hierarchy of memory stores based on varying access speeds to cache data. Highly requested data is cached in high-speed access memory stores, allowing swifter access by central processing unit (CPU) cores. Cache hierarchy is a form and part of memory hierarchy and can be considered a form of tiered storage. This design was intended to allow CPU cores to process faster despite the CAS latency, memory latency of computer data storage, main memory access. Accessing main memory can act as a bottleneck for computer performance, CPU core performance as the CPU waits for data, while making all of main memory high-speed may be prohibitively expensive. High-speed caches are a compromise allowing high-speed access to the data most-used by the CPU, permitting a faster clock rate, CPU clock. Background In the history of computer and electronic chip development, there was a period when increases in CPU speed outpaced ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Single Instruction, Multiple Data

Single instruction, multiple data (SIMD) is a type of parallel computer, parallel processing in Flynn's taxonomy. SIMD describes computers with multiple processing elements that perform the same operation on multiple data points simultaneously. SIMD can be internal (part of the hardware design) and it can be directly accessible through an instruction set architecture (ISA), but it should not be confused with an ISA. Such machines exploit Data parallelism, data level parallelism, but not Concurrent computing, concurrency: there are simultaneous (parallel) computations, but each unit performs exactly the same instruction at any given moment (just with different data). A simple example is to add many pairs of numbers together, all of the SIMD units are performing an addition, but each one has different pairs of values to add. SIMD is particularly applicable to common tasks such as adjusting the contrast in a digital image or adjusting the volume of digital audio. Most modern Cen ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Arrow Lake (microprocessor)

Arrow Lake is the codename for Core Ultra Series 2 processors designed by Intel, released on October 24, 2024. It follows on from Meteor Lake which saw Intel move from monolithic silicon to a disaggregated MCM design. Meteor Lake was limited to a mobile release while Arrow Lake includes both socketable desktop processors and mainstream and enthusiast mobile processors. Core Ultra 200H and 200HX series mobile processors will follow in early 2025. Arrow Lake desktop CPUs integrated Thunderbolt 4 and USB4 support in the CPU, which allowed it to not be limited by PCIe 3.0 speeds and use simple re-timers instead. The chipset has the same maximum five integrated USB 3.2 2x2, and is Thunderbolt 5 ready if a discrete board is used. The integrated GPU added HDMI 2.1 FRL 48 Gbit/s (also in Meteor Lake) and variable refresh rate (VRR) support. CU-DIMM DDR5 memory support was added and is needed for optimal performance. Background The first official mention of Arrow Lake came on February ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |