|

GAL22V10

The GAL22V10 is a series of programmable-logic devices from Lattice Semiconductor, implemented as CMOS-based generic array logic ICs, and available in dual inline packages or plastic leaded chip carriers. It is an example of a standard production GAL device that is often used in educational settings as a basic programmable-logic device. Specifications The GAL22V10 has 12 input pins, and 10 pins that can be configured as either inputs or outputs, and exists in various switching speeds, from 25 to 4 ns. Each output is driven by an output-logic macrocell (OLMC), with an output-enable product term, and a variable number of product terms, ranging from eight to sixteen. Each OLMC may be set to output as inverting or non-inverting, and be placed into either registered or combinatorial mode. In registered mode, each macrocell actively uses a D-flip-flop to hold a state under control of the data input from the logic portion of the macrocell and the rising edge of the clock signal, w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Lattice Semiconductor

Lattice Semiconductor Corporation is an American semiconductor company specializing in the design and manufacturing of low power, field-programmable gate arrays (FPGAs). Headquartered in the Silicon Forest area of Hillsboro, Oregon, the company also has operations in Shanghai, Manila, and Singapore. Lattice Semiconductor has more than 700 employees and an annual revenue of more than $400 million as of 2019. Founded in 1983, the company went public in 1989 and is traded on the NASDAQ stock exchange under the symbol LSCC. History Founding and early growth Lattice was founded on April 3, 1983, by C. Norman Winningstad, Rahul Sud, and Ray Capece, with investment from Winningstad, Harry Merlo, Tom Moyer, and John Piacentini. Lattice was incorporated in Oregon in 1983 and reincorporated in Delaware in 1985. Co-founder Sud left as president in December 1986, and Winningstad left in 1991 as chairman of the board. Early struggles led to chapter 11 bankruptcy reorganization in July 1 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Generic Array Logic

The Generic Array Logic (also known as GAL and sometimes as gate array logic) device was an innovation of the PAL and was invented by Lattice Semiconductor. The GAL was an improvement on the PAL because one device type was able to take the place of many PAL device types or could even have functionality not covered by the original range of PAL devices. Its primary benefit, however, was that it was erasable and re-programmable, making prototyping and design changes easier for engineers. A similar device called a PEEL (programmable electrically erasable logic) was introduced by the International CMOS Technology (ICT) corporation. See also * Programmable logic device (PLD) ** Complex programmable logic device (CPLD) ** Erasable programmable logic device (EPLD) * GAL22V10 The GAL22V10 is a series of programmable-logic devices from Lattice Semiconductor, implemented as CMOS-based generic array logic ICs, and available in dual inline packages or plastic leaded chip carriers. It ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Programmable-logic Device

A programmable logic device (PLD) is an electronic component used to build reconfigurable digital circuits. Unlike digital logic constructed using discrete logic gates with fixed functions, a PLD has an undefined function at the time of manufacture. Before the PLD can be used in a circuit it must be programmed to implement the desired function. Compared to fixed logic devices, programmable logic devices simplify the design of complex logic and may offer superior performance. Unlike for microprocessors, programming a PLD changes the connections made between the gates in the device. PLDs can broadly be categorised into, in increasing order of complexity, Simple Programmable Logic Devices (SPLDs), comprising programmable array logic, programmable logic array and generic array logic; Complex Programmable Logic Devices (CPLDs) and Field-Programmable Gate Arrays (FPGAs). History In 1969, Motorola offered the XC157, a mask-programmed gate array with 12 gates and 30 uncommit ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Dual Inline Package

In microelectronics, a dual in-line package (DIP or DIL), is an electronic component package with a rectangular housing and two parallel rows of electrical connecting pins. The package may be through-hole mounted to a printed circuit board (PCB) or inserted in a socket. The dual-inline format was invented by Don Forbes, Rex Rice and Bryant Rogers at Fairchild R&D in 1964, when the restricted number of leads available on circular transistor-style packages became a limitation in the use of integrated circuits. Increasingly complex circuits required more signal and power supply leads (as observed in Rent's rule); eventually microprocessors and similar complex devices required more leads than could be put on a DIP package, leading to development of higher-density chip carriers. Furthermore, square and rectangular packages made it easier to route printed-circuit traces beneath the packages. A DIP is usually referred to as a DIP''n'', where ''n'' is the total number of pins. For ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Plastic Leaded Chip Carrier

In electronics, a chip carrier is one of several kinds of surface-mount technology packages for integrated circuits (commonly called "chips"). Connections are made on all four edges of a square package; compared to the internal cavity for mounting the integrated circuit, the package overall size is large.Kenneth Jackson, Wolfgang Schroter, (ed), ''Handbook of Semiconductor Technology Volume 2'',Wiley VCH, 2000, ,page 627 Types Chip carriers may have either J-shaped metal leads for connections by solder or by a socket, or may be lead-less with metal pads for connections. If the leads extend beyond the package, the preferred description is "flat pack". Chip carriers can be smaller than dual in-line packages and since they use all four edges of the package they can have a larger pin count. Chip carriers may be made of ceramic or plastic. Some forms of chip carrier package are standardized in dimensions and registered with trade industry associations such as JEDEC. Other forms a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

EEPROM

EEPROM (also called E2PROM) stands for electrically erasable programmable read-only memory and is a type of non-volatile memory used in computers, usually integrated in microcontrollers such as smart cards and remote keyless systems, or as a separate chip device to store relatively small amounts of data by allowing individual bytes to be erased and reprogrammed. EEPROMs are organized as arrays of floating-gate transistors. EEPROMs can be programmed and erased in-circuit, by applying special programming signals. Originally, EEPROMs were limited to single-byte operations, which made them slower, but modern EEPROMs allow multi-byte page operations. An EEPROM has a limited life for erasing and reprogramming, now reaching a million operations in modern EEPROMs. In an EEPROM that is frequently reprogrammed, the life of the EEPROM is an important design consideration. Flash memory is a type of EEPROM designed for high speed and high density, at the expense of large erase blocks ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

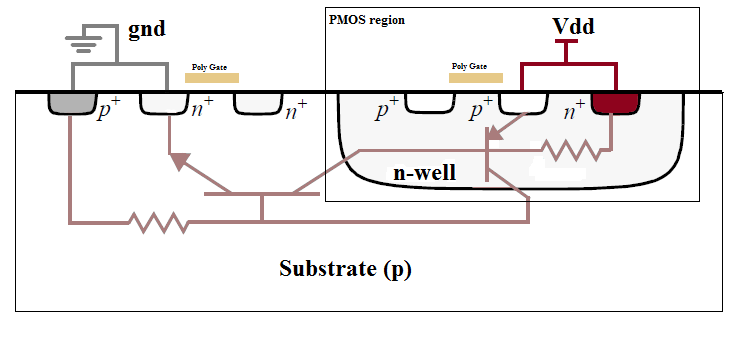

Latch-up Protection

A latch-up is a type of short circuit which can occur in an integrated circuit (IC). More specifically it is the inadvertent creation of a low- impedance path between the power supply rails of a MOSFET circuit, triggering a parasitic structure which disrupts proper functioning of the part, possibly even leading to its destruction due to overcurrent. A power cycle is required to correct this situation. The parasitic structure is usually equivalent to a thyristor (or SCR), a PNPN structure which acts as a PNP and an NPN transistor stacked next to each other. During a latch-up when one of the transistors is conducting, the other one begins conducting too. They both keep each other in saturation for as long as the structure is forward-biased and some current flows through it - which usually means until a power-down. The SCR parasitic structure is formed as a part of the totem-pole PMOS and NMOS transistor pair on the output drivers of the gates. The latch-up does not have to happe ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Charge Pump

A charge pump is a kind of DC-to-DC converter that uses capacitors for energetic charge storage to raise or lower voltage. Charge-pump circuits are capable of high efficiencies, sometimes as high as 90–95%, while being electrically simple circuits. Description Charge pumps use some form of switching device to control the connection of a supply voltage across a load through a capacitor. In a two stage cycle, in the first stage a capacitor is connected across the supply, charging it to that same voltage. In the second stage the circuit is reconfigured so that the capacitor is in series with the supply and the load. This doubles the voltage across the load - the sum of the original supply and the capacitor voltages. The pulsing nature of the higher voltage switched output is often smoothed by the use of an output capacitor. An external or secondary circuit drives the switching, typically at tens of kilohertz up to several megahertz. The high frequency minimizes the amount of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |