|

Knights Corner (Intel)

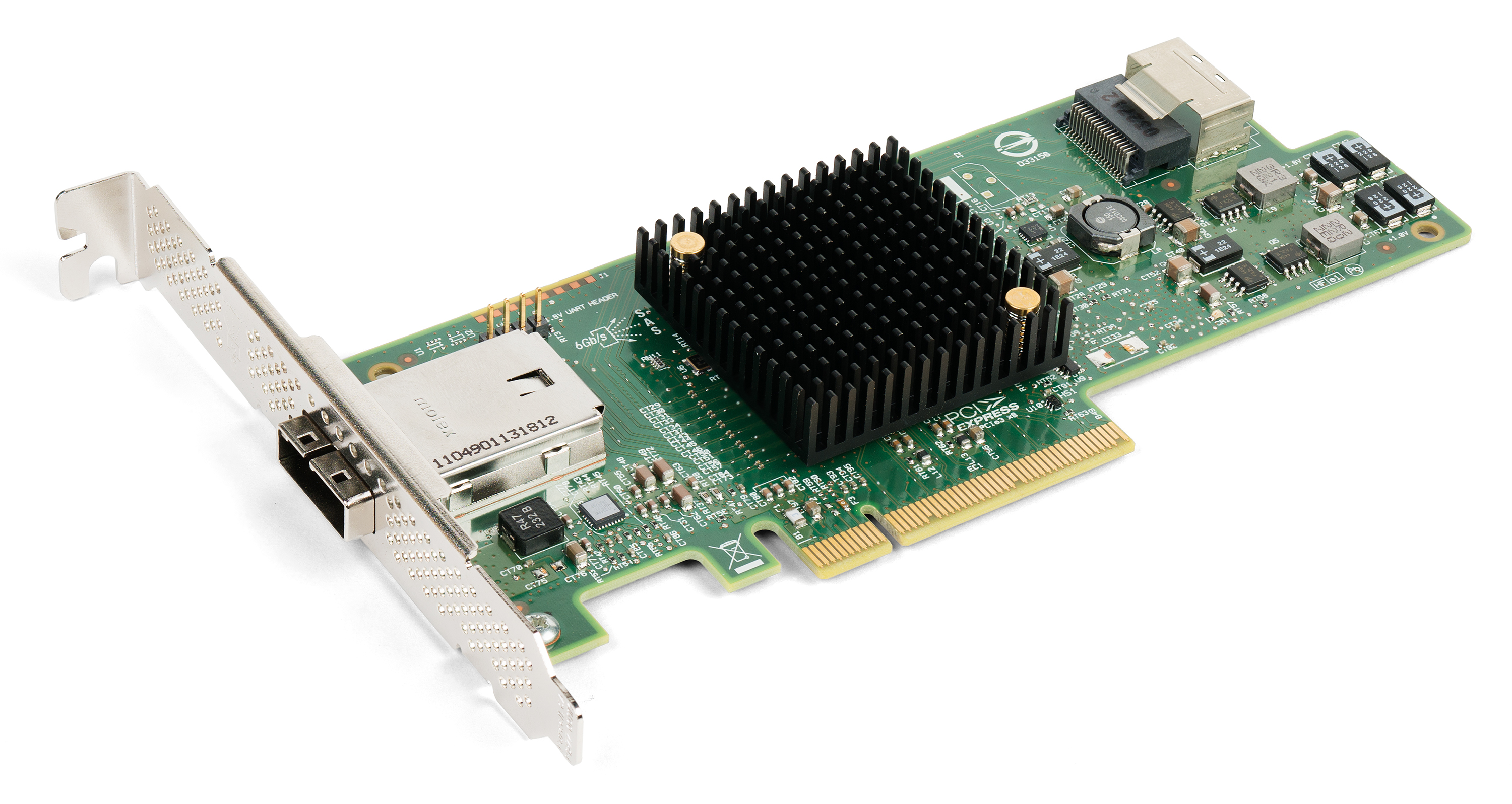

Xeon Phi is a discontinued series of x86 manycore processors designed and made by Intel. It was intended for use in supercomputers, servers, and high-end workstations. Its architecture allowed use of standard programming languages and application programming interfaces (APIs) such as OpenMP. Xeon Phi launched in 2010. Since it was originally based on an earlier GPU design ( codenamed "Larrabee") by Intel that was cancelled in 2009, it shared application areas with GPUs. The main difference between Xeon Phi and a GPGPU like Nvidia Tesla was that Xeon Phi, with an x86-compatible core, could, with less modification, run software that was originally targeted to a standard x86 CPU. Initially in the form of PCI Express-based add-on cards, a second-generation product, codenamed ''Knights Landing'', was announced in June 2013. These second-generation chips could be used as a standalone CPU, rather than just as an add-in card. In June 2013, the Tianhe-2 supercomputer at the National S ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Xenos (graphics Chip)

The Xenos is a custom graphics processing unit (GPU) designed by ATI (now taken over by AMD), used in the Xbox 360 video game console developed and produced for Microsoft. Developed under the codename "C1", it is in many ways related to the R520 architecture and therefore very similar to an ATI Radeon X1800 XT series of PC graphics cards as far as features and performance are concerned. However, the Xenos introduced new design ideas that were later adopted in the TeraScale microarchitecture, such as the unified shader architecture. The package contains two separate dies, the GPU and an eDRAM (manufactured by NEC), featuring a total of 337 million transistors. Specifications The TeraScale microarchitecture is based on this chip, the shader units are organized in three SIMD groups with 16 processors per group, for a total of 48 processors. Each of these processors is composed of a 5-wide vector unit (total 5 FP32 ALUs), resulting in 240 units, that can serially execute up to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Manycore Processor

Manycore processors are special kinds of multi-core processors designed for a high degree of parallel processing, containing numerous simpler, independent processor cores (from a few tens of cores to thousands or more). Manycore processors are used extensively in embedded computers and high-performance computing. Contrast with multicore architecture Manycore processors are distinct from multi-core processors in being optimized from the outset for a higher degree of explicit parallelism, and for higher throughput (or lower power consumption) at the expense of latency and lower single-thread performance. The broader category of multi-core processors, by contrast, are usually designed to efficiently run ''both'' parallel ''and'' serial code, and therefore place more emphasis on high single-thread performance (e.g. devoting more silicon to out-of-order execution, deeper pipelines, more superscalar execution units, and larger, more general caches), and shared memory. These techn ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ivy Bridge (microarchitecture)

Ivy Bridge is the codename for Intel's 22 nm microarchitecture used in the third generation of the Intel Core processors ( Core i7, i5, i3). Ivy Bridge is a die shrink to 22 nm process based on FinFET ("3D") Tri-Gate transistors, from the former generation's 32 nm Sandy Bridge microarchitecture—also known as tick–tock model. The name is also applied more broadly to the Xeon and Core i7 Extreme Ivy Bridge-E series of processors released in 2013. Ivy Bridge processors are backward compatible with the Sandy Bridge platform, but such systems might require a firmware update (vendor specific). In 2011, Intel released the 7-series Panther Point chipsets with integrated USB 3.0 and SATA 3.0 to complement Ivy Bridge. Volume production of Ivy Bridge chips began in the third quarter of 2011. Quad-core and dual-core-mobile models launched on April 29, 2012 and May 31, 2012 respectively. Core i3 desktop processors, as well as the first 22 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

National Supercomputer Center In Guangzhou

The National Supercomputer Center in Guangzhou houses Tianhe-2, which is currently the seventh fastest supercomputer in the world, with a measured 33.86 petaflop/s (quadrillions of calculations per second). Tianhe-2 is operated by the National University of Defence Technology, and owned by the Chinese government. See also * Supercomputing in China * National Supercomputing Center of Tianjin * National Supercomputing Center (Shenzhen) * Shanghai Supercomputer Center References External linksNational Supercomputing Center in Guangzhou Guangzhou Computer science institutes in China Science and technology in China Supercomputer sites Supercomputing in China 2014 establishments in China 2014 in Guangzhou {{China-struct-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tianhe-2

Tianhe-2 or TH-2 (, i.e. 'Milky Way 2') is a 33.86- petaflop supercomputer located in the National Supercomputer Center in Guangzhou, China. It was developed by a team of 1,300 scientists and engineers. It was the world's fastest supercomputer according to the TOP500 lists for June 2013, November 2013, June 2014, November 2014, June 2015, and November 2015. The record was surpassed in June 2016 by the Sunway TaihuLight. In 2015, plans by Sun Yat-sen University in collaboration with Guangzhou district and city administration to double its computing capacities were stopped by a U.S. government rejection of Intel's application for an export license for the CPUs and coprocessor boards. In response to the U.S. sanctions, China introduced the Sunway TaihuLight supercomputer in 2016, which substantially outperforms the Tianhe-2 (and also affected the update of Tianhe-2 to Tianhe-2A, replacing U.S. tech), and in November 2022 ranks eighth in the TOP500 list while using completely do ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IEEE Micro

''IEEE Micro'' is a bimonthly peer-reviewed scientific journal published by the IEEE Computer Society covering small systems and semiconductor chips, including integrated circuit processes and practices, project management, development tools and infrastructure, as well as chip design and architecture, empirical evaluations of small system and IC technologies and techniques, and human and social aspects of system development. Editors-in-chief The following people are or have been editor-in-chief: * 2024–present: Hsien-Hsin Sean Lee * 2019–2023: Lizy Kurian John * 2015–2018: Lieven Eeckhout * 2011–2014: Erik R. Altman * 2007–2010: David H. Albonesi * 2003–2006: Pradip Bose * 1999–2001: Ken Sakamura * 1995–1998: Steve Diamond * 1991–1994: Dante Del Corso * 1987–1990: Joe Hootman * 1985–1987: James J. Farrell III * 1983–1984: Peter Rony and Tom Cain * 1980–1982: Richard C. Jaeger External links * Micro Micro may refer to: Measurement * ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe, is a high-speed standard used to connect hardware components inside computers. It is designed to replace older expansion bus standards such as Peripheral Component Interconnect, PCI, PCI-X and Accelerated Graphics Port, AGP. Developed and maintained by the PCI-SIG (PCI Special Interest Group), PCIe is commonly used to connect graphics cards, sound cards, Wi-Fi and Ethernet adapters, and storage devices such as solid-state drives and hard disk drives. Compared to earlier standards, PCIe supports faster data transfer, uses fewer pins, takes up less space, and allows devices to be added or removed while the computer is running (hot swapping). It also includes better error detection and supports newer features like I/O virtualization for advanced computing needs. PCIe connections are made through "lanes," which are pairs of wires that send and receive data. Devices can use one or more lanes ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nvidia Tesla

Nvidia Tesla is the former name for a line of products developed by Nvidia targeted at stream processing or GPGPU, general-purpose graphics processing units (GPGPU), named after pioneering electrical engineer Nikola Tesla. Its products began using GPUs from the GeForce 8 series, G80 series, and have continued to accompany the release of new chips. They are programmable using the CUDA or OpenCL application programming interface, APIs. The Nvidia Tesla product line competed with AMD's Radeon Instinct and Intel Xeon Phi lines of deep learning and GPU cards. Nvidia retired the Tesla brand in May 2020, reportedly because of potential confusion with the Tesla, Inc., brand of cars. Its new GPUs are branded Nvidia Data Center GPUs as in the Ampere (microarchitecture), Ampere-based A100 GPU. Nvidia DGX servers feature Nvidia GPGPUs. Overview Offering computational power much greater than traditional Central processing units, microprocessors, the Tesla products targeted the high-perfo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GPGPU

General-purpose computing on graphics processing units (GPGPU, or less often GPGP) is the use of a graphics processing unit (GPU), which typically handles computation only for computer graphics, to perform computation in applications traditionally handled by the central processing unit (CPU). The use of multiple video cards in one computer, or large numbers of graphics chips, further parallelizes the already parallel nature of graphics processing. Essentially, a GPGPU pipeline is a kind of parallel processing between one or more GPUs and CPUs that analyzes data as if it were in image or other graphic form. While GPUs operate at lower frequencies, they typically have many times the number of cores. Thus, GPUs can process far more pictures and graphical data per second than a traditional CPU. Migrating data into graphical form and then using the GPU to scan and analyze it can create a large speedup. GPGPU pipelines were developed at the beginning of the 21st century for grap ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Reuters

Reuters ( ) is a news agency owned by Thomson Reuters. It employs around 2,500 journalists and 600 photojournalists in about 200 locations worldwide writing in 16 languages. Reuters is one of the largest news agencies in the world. The agency was established in London in 1851 by Paul Reuter. The Thomson Corporation of Canada acquired the agency in a 2008 corporate merger, resulting in the formation of the Thomson Reuters Corporation. In December 2024, Reuters was ranked as the 27th most visited news site in the world, with over 105 million monthly readers. History 19th century Paul Julius Reuter worked at a book-publishing firm in Berlin and was involved in distributing radical pamphlets at the beginning of the Revolutions of 1848. These publications brought much attention to Reuter, who in 1850 developed a prototype news service in Aachen using homing pigeons and electric telegraphy from 1851 on, in order to transmit messages between Brussels and Aachen, in what today is Aa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ExtremeTech

ExtremeTech is a technology weblog, launched in June 2001, which focuses on hardware, computer software, science, and other technologies. Between 2003 and 2005, ExtremeTech was also a print magazine and the publisher of a popular series of how-to and do-it-yourself books. Background ExtremeTech was launched as a website in June 2001, with co-founder Bill Machrone as Editor-in-Chief, and fellow co-founder Nick Stam as Senior Technical Director. Loyd Case, Dave Salvator, Mark Hachman, and Jim Lynch were other original core ET staff. In 2002 Jim Louderback became the Editor-in-Chief. When initially launched, ExtremeTech covered a broad range of technical topics with very in-depth technical stories. Topic areas included core PC techniques (CPUs/GPUs), networking, operating systems, software development, display technology, printers, scanners, etc. By 2003, Ziff Davis management wanted to reduce expenses and cut back content to core PC tech areas, focusing on how to build and opt ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Morgan Kaufmann

Morgan Kaufmann Publishers is a Burlington, Massachusetts (San Francisco, California until 2008) based publisher specializing in computer science and engineering content. Since 1984, Morgan Kaufmann has been publishing contents on information technology, computer architecture, data management, computer networking, computer systems, human computer interaction, computer graphics, multimedia information and systems, artificial intelligence, computer security, and software engineering. Morgan Kaufmann's audience includes the research and development communities, information technology (IS/IT) managers, and students in professional degree programs. The company was founded in 1984 by publishers Michael B. Morgan and William Kaufmann and computer scientist Nils Nilsson. It was held privately until 1998, when it was acquired by Harcourt General and became an imprint of the Academic Press, a subsidiary of Harcourt. Harcourt was acquired by Reed Elsevier in 2001; Morgan Kaufmann is now ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |