|

GDDR4

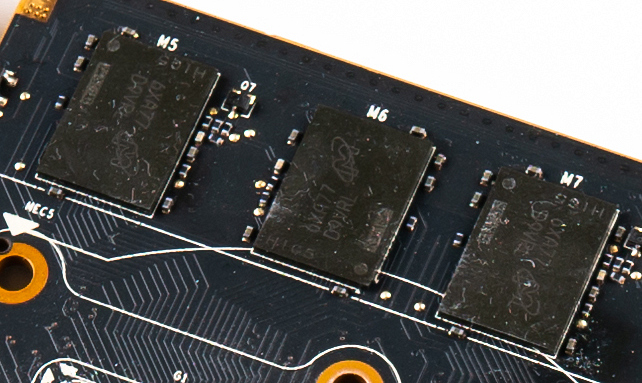

GDDR4 SDRAM, an abbreviation for Graphics Double Data Rate 4 Synchronous Dynamic Random-Access Memory, is a type of graphics card memory (SGRAM) specified by the JEDEC Semiconductor Memory Standard. It is a rival medium to Rambus's XDR DRAM. GDDR4 is based on DDR3 SDRAM technology and was intended to replace the DDR2-based GDDR3, but it ended up being replaced by GDDR5 within a year. History * On October 26, 2005, Samsung announced that it developed the first GDDR4 memory, a 256- Mbit chip running at 2.5 Gbit/s. Samsung also revealed plans to sample and mass-produce GDDR4 SDRAM rated at 2.8 Gbit/s per pin. * In 2005, Hynix developed the first 512-Mbit GDDR4 memory chip. * On February 14, 2006, Samsung announced the development of 32-bit 512-Mbit GDDR4 SDRAM capable of transferring 3.2 Gbit/s per pin, or 12.8 GB/s for the module. * On July 5, 2006, Samsung announced the mass-production of 32-bit 512-Mbit GDDR4 SDRAM rated at 2.4 Gbit/s per pin, or 9.6& ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SDRAM

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to the early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions delayed only by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''banks'', allowing the device to operate on a memor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Prefetch Buffer

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any Dynamic random-access memory, DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to the early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions delayed only by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''Memory bank, banks'', a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SGRAM

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to the early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions delayed only by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''banks'', allowing the device to operate on a memory a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GDDR5

Graphics Double Data Rate 5 Synchronous Dynamic Random-Access Memory (GDDR5 SDRAM) is a type of synchronous graphics random-access memory (SGRAM) with a high bandwidth ("double data rate") interface designed for use in graphics cards, game consoles, and high-performance computing. It is a type of GDDR SDRAM (graphics DDR SDRAM). Overview Like its predecessor, GDDR4, GDDR5 is based on DDR3 SDRAM memory, which has double the data lines compared to DDR2 SDRAM. GDDR5 also uses 8-bit wide prefetch buffers similar to GDDR4 and DDR3 SDRAM. GDDR5 SGRAM conforms to the standards which were set out in the GDDR5 specification by the JEDEC. SGRAM is single-ported. However, it can open two memory pages at once, which simulates the dual-port nature of other VRAM technologies. It uses an 8N- prefetch architecture and DDR interface to achieve high performance operation and can be configured to operate in ×32 mode or ×16 (clamshell) mode which is detected during device initializati ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GDDR5 SDRAM

Graphics Double Data Rate 5 Synchronous Dynamic Random-Access Memory (GDDR5 SDRAM) is a type of Synchronous dynamic random-access memory#Synchronous graphics RAM .28SGRAM.29, synchronous graphics random-access memory (SGRAM) with a high Bandwidth (computing), bandwidth ("double data rate") interface designed for use in Video card, graphics cards, Video game console, game consoles, and high-performance computing. It is a type of GDDR SDRAM (graphics DDR SDRAM). Overview Like its predecessor, GDDR4, GDDR5 is based on DDR3 SDRAM memory, which has double the data lines compared to DDR2 SDRAM. GDDR5 also uses 8-bit wide prefetch buffers similar to GDDR4 and DDR3 SDRAM. GDDR5 Dynamic random-access memory#Synchronous graphics RAM, SGRAM conforms to the standards which were set out in the GDDR5 specification by the JEDEC. SGRAM is single-ported. However, it can open two memory pages at once, which simulates the dual-port nature of other VRAM technologies. It uses an 8N-Prefetch buff ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Graphics Card

A graphics card (also called a video card, display card, graphics accelerator, graphics adapter, VGA card/VGA, video adapter, display adapter, or colloquially GPU) is a computer expansion card that generates a feed of graphics output to a display device such as a computer monitor, monitor. Graphics cards are sometimes called ''discrete'' or ''dedicated'' graphics cards to emphasize their distinction to an graphics processing unit#Integrated graphics processing unit, integrated graphics processor on the motherboard or the central processing unit (CPU). A graphics processing unit (GPU) that performs the necessary computations is the main component in a graphics card, but the acronym "GPU" is sometimes also used to refer to the graphics card as a whole erroneously. Most graphics cards are not limited to simple display output. The graphics processing unit can be used for additional processing, which reduces the load from the CPU. Additionally, computing platforms such as OpenCL and C ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

XDR DRAM

XDR DRAM (extreme data rate dynamic random-access memory) is a high-performance dynamic random-access memory interface. It is based on and succeeds RDRAM. Competing technologies include DDR2 and GDDR4. Overview XDR was designed to be effective in small, high-bandwidth consumer systems, high-performance memory applications, and high-end GPUs. It eliminates the unusually high latency problems that plagued early forms of RDRAM. Also, XDR DRAM has heavy emphasis on per-pin bandwidth, which can benefit further cost control on PCB production. This is because fewer lanes are needed for the same amount of bandwidth. Rambus owns the rights to the technology. XDR is used by Sony in the PlayStation 3 console. Technical specifications Performance * Initial clock rate at 400 MHz. * (ODR): Eight bits per clock cycle per lane. * Each chip provides 8, 16, or 32 programmable lanes, providing up to 230.4 Gbit/s (28.8 GB/s) at 900 MHz (7.2 GHz effective). Feat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GDDR3

GDDR3 SDRAM (Graphics Double Data Rate 3 SDRAM) is a type of DDR SDRAM specialized for graphics processing units (GPUs) offering less access latency and greater device bandwidths compared to DDR2 SDRAM of the same generation. Its specification was developed by ATI Technologies in collaboration with DRAM vendors including Elpida Memory, Hynix Semiconductor, Infineon (later Qimonda) and Micron. It was later adopted as a JEDEC standard. Overview It has much the same technological base as DDR2, but the power and heat dispersal requirements have been reduced somewhat, allowing for higher performance memory modules, and simplified cooling systems. GDDR3 is not related to the JEDEC DDR3 specification. This memory uses internal terminators, enabling it to better handle certain graphics demands. To improve throughput, GDDR3 memory transfers 4 bits of data per pin in 2 clock cycles. The GDDR3 interface transfers two 32 bit wide data words per clock cycle from the I/O pins. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of Interface Bit Rates

A list is a set of discrete items of information collected and set forth in some format for utility, entertainment, or other purposes. A list may be memorialized in any number of ways, including existing only in the mind of the list-maker, but lists are frequently written down on paper, or maintained electronically. Lists are "most frequently a tool", and "one does not ''read'' but only ''uses'' a list: one looks up the relevant information in it, but usually does not need to deal with it as a whole". Lucie Doležalová,The Potential and Limitations of Studying Lists, in Lucie Doležalová, ed., ''The Charm of a List: From the Sumerians to Computerised Data Processing'' (2009). Purpose It has been observed that, with a few exceptions, "the scholarship on lists remains fragmented". David Wallechinsky, a co-author of '' The Book of Lists'', described the attraction of lists as being "because we live in an era of overstimulation, especially in terms of information, and lists help ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Infineon

Infineon Semiconductor solutions is the largest microcontroller manufacturer in the world, as well as Germany's largest semiconductor manufacturer. It is also the leading automotive semiconductor manufacturer globally. Infineon had roughly 58,000 employees in 2024 and is one of the ten largest semiconductor manufacturers worldwide. The company was spun-off from Siemens AG in 1999. In 2024 the company achieved sales of approximately €15 billion. Markets Infineon markets semiconductors and systems for automotive, industrial, and multimarket sectors, as well as chip card and security products. Infineon has subsidiaries in the US in Milpitas, California and in the Asia-Pacific region, in Singapore, and Tokyo. Infineon has a number of facilities in Europe, one in Dresden, Germany. Infineon's high power segment is in Warstein, Germany; Villach, Graz and Linz in Austria; Cegléd in Hungary; and Italy. It also operates R&D centers in France, Singapore, Romania, Taiwan, U ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |