|

GDDR3

GDDR3 SDRAM (Graphics Double Data Rate 3 SDRAM) is a type of DDR SDRAM specialized for graphics processing units (GPUs) offering less access latency and greater device bandwidths compared to DDR2 SDRAM of the same generation. Its specification was developed by ATI Technologies in collaboration with DRAM vendors including Elpida Memory, Hynix Semiconductor, Infineon (later Qimonda) and Micron. It was later adopted as a JEDEC standard. Overview It has much the same technological base as DDR2, but the power and heat dispersal requirements have been reduced somewhat, allowing for higher performance memory modules, and simplified cooling systems. GDDR3 is not related to the JEDEC DDR3 specification. This memory uses internal terminators, enabling it to better handle certain graphics demands. To improve throughput, GDDR3 memory transfers 4 bits of data per pin in 2 clock cycles. The GDDR3 interface transfers two 32 bit wide data words per clock cycle from the I/O pins. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD Radeon HD 4670

The Radeon R700 is the engineering codename for a graphics processing unit series developed by Advanced Micro Devices under the ATI brand name. The foundation chip, codenamed ''RV770'', was announced and demonstrated on June 16, 2008 as part of the FireStream 9250 and Cinema 2.0 initiative launch media event, with official release of the Radeon HD 4800 series on June 25, 2008. Other variants include enthusiast-oriented RV790, mainstream product RV730, RV740 and entry-level RV710. Its direct competition was NVIDIA's GeForce 200 series, which launched in the same month. Architecture This article is about all products under the brand "Radeon HD 4000 Series". All products implement TeraScale 1 microarchitecture. Execution units The RV770 extends the R600's unified shader architecture by increasing the stream processing unit count to 800 units (up from 320 units in the R600), which are grouped into 10 ''SIMD cores'' composed of 16 ''shader cores'' containing 4 FP MADD/DP ALUs an ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Synchronous Dynamic Random-access Memory

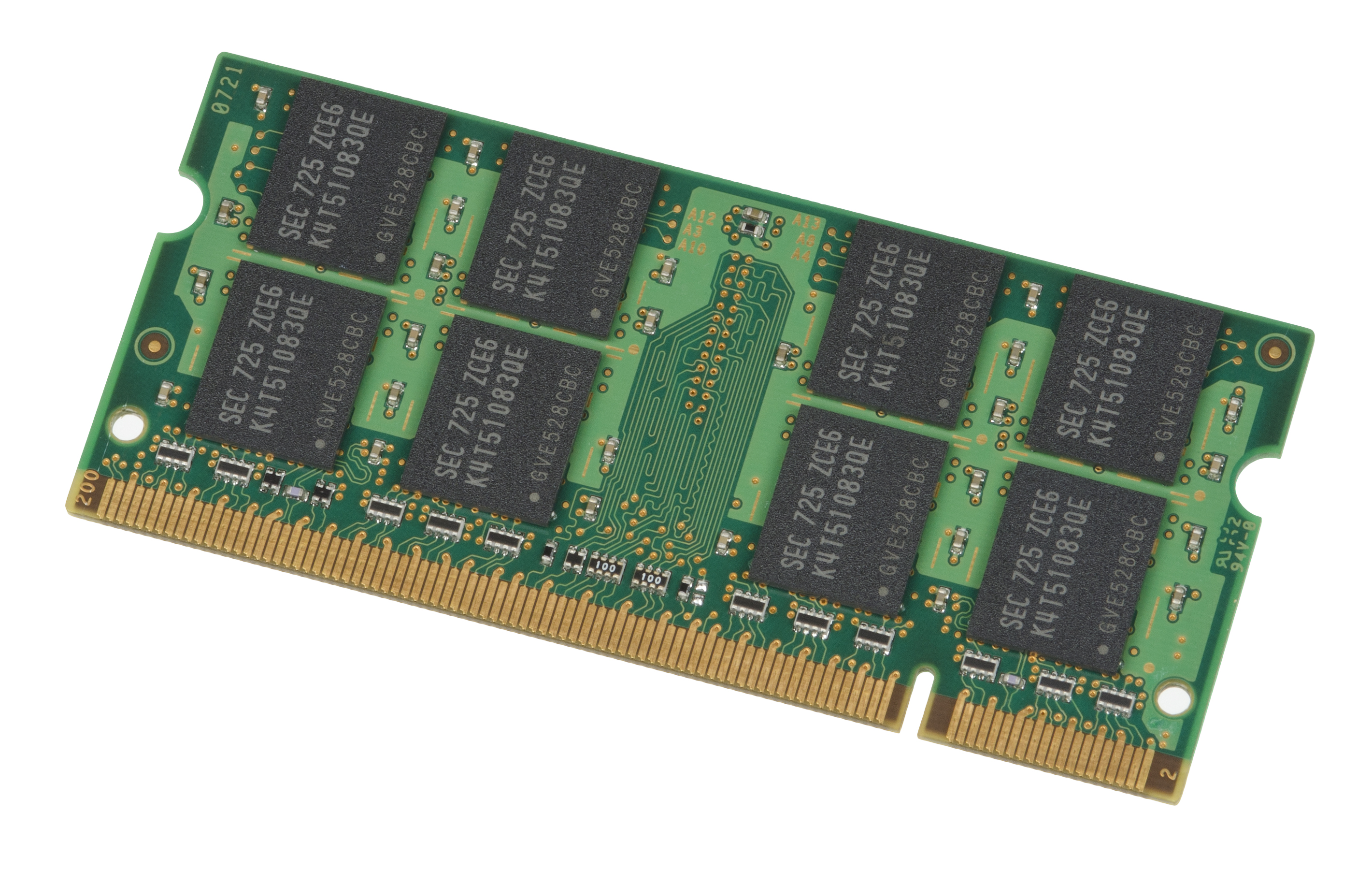

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to the early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions delayed only by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''banks'', allowing the device to operate on a memor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GDDR4 SDRAM

GDDR4 SDRAM, an abbreviation for Graphics Double Data Rate 4 Synchronous Dynamic Random-Access Memory, is a type of graphics card memory (SGRAM) specified by the JEDEC Semiconductor Memory Standard. It is a rival medium to Rambus's XDR DRAM. GDDR4 is based on DDR3 SDRAM technology and was intended to replace the DDR2-based GDDR3, but it ended up being replaced by GDDR5 within a year. History * On October 26, 2005, Samsung announced that it developed the first GDDR4 memory, a 256- Mbit chip running at 2.5 Gbit/s. Samsung also revealed plans to sample and mass-produce GDDR4 SDRAM rated at 2.8 Gbit/s per pin. * In 2005, Hynix developed the first 512-Mbit GDDR4 memory chip. * On February 14, 2006, Samsung announced the development of 32-bit 512-Mbit GDDR4 SDRAM capable of transferring 3.2 Gbit/s per pin, or 12.8 GB/s for the module. * On July 5, 2006, Samsung announced the mass-production of 32-bit 512-Mbit GDDR4 SDRAM rated at 2.4 Gbit/s per pin, or 9.6& ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GeForce FX

The GeForce FX or "GeForce 5" series (codenamed NV30) is a line of graphics processing units from the manufacturer Nvidia. Overview Nvidia's GeForce FX series is the fifth generation of the GeForce line. With GeForce 3, the company introduced programmable shader functionality into their 3D architecture, in line with the release of Microsoft's DirectX 8.0. The GeForce 4 Ti was an enhancement of the GeForce 3 technology. With real-time 3D graphics technology continually advancing, the release of DirectX 9.0 brought further refinement of programmable pipeline technology with the arrival of Shader Model 2.0. The GeForce FX series is Nvidia's first generation Direct3D 9-compliant hardware. The series was manufactured on TSMC's 130 nm fabrication process. It is compliant with Shader Model 2.0/2.0A, allowing more flexibility in complex shader/fragment programs and much higher arithmetic precision. It supports a number of new memory technologies, including DDR2, GDDR2 and GDDR3 a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GDDR2

Double Data Rate 2 Synchronous Dynamic Random-Access Memory (DDR2 SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) interface. It is a JEDEC standard (JESD79-2); first published in September 2003. DDR2 succeeded the original DDR SDRAM specification, and was itself succeeded by DDR3 SDRAM in 2007. DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR. In addition to double pumping the data bus as in DDR SDRAM (transferring data on the rising and falling edges of the bus clock signal), DDR2 allows higher bus speed and requires lower power by running the internal clock at half the speed of the data bus. The two factors combine to produce a total of four data transfers per internal clock cycle. Since the DDR2 internal clock runs at half the DDR external clock rate, DDR2 memory operating at the same external data bus clock rate as DDR results in DDR2 being able to provide the same bandwidth but with better lat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Qimonda

Qimonda Aktiengesellschaft, AG ( ) was a German DRAM, memory company split out of Infineon Technologies (itself a spun off business unit of Siemens AG) on 1 May 2006 to form at the time the second largest DRAM company worldwide, according to the industry research firm Gartner Dataquest. It was a patent licensing firm until Micron and others purchased its patents. Headquartered in Munich, Qimonda was a Wafer (electronics)#Standard_wafer_sizes, 300 mm manufacturer and was one of the top suppliers of DRAM products for the personal computer, PC and server (computing), server markets. Infineon still controls a 77.5% stake, which it has written down (2008). Infineon was on record as having the aim of divesting itself of this stake, with the purpose of becoming a minority stakeholder in 2009. The company has issued 42 million American depositary receipt, ADR shares, each ADR share representing one ordinary share in Qimonda. At its height in 2007, Qimonda employed approximately 13,50 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR2 SDRAM

Double Data Rate 2 Synchronous Dynamic Random-Access Memory (DDR2 SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) interface. It is a JEDEC standard (JESD79-2); first published in September 2003. DDR2 succeeded the original DDR SDRAM specification, and was itself succeeded by DDR3 SDRAM in 2007. DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR. In addition to double pumping the data bus as in DDR SDRAM (transferring data on the rising and falling edges of the bus clock signal), DDR2 allows higher bus speed and requires lower power by running the internal clock at half the speed of the data bus. The two factors combine to produce a total of four data transfers per internal clock cycle. Since the DDR2 internal clock runs at half the DDR external clock rate, DDR2 memory operating at the same external data bus clock rate as DDR results in DDR2 being able to provide the same bandwidth but with better la ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GDDR2 SDRAM

Double Data Rate 2 Synchronous Dynamic Random-Access Memory (DDR2 SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) interface. It is a JEDEC standard (JESD79-2); first published in September 2003. DDR2 succeeded the original DDR SDRAM specification, and was itself succeeded by DDR3 SDRAM in 2007. DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR. In addition to double pumping the data bus as in DDR SDRAM (transferring data on the rising and falling edges of the bus clock signal), DDR2 allows higher bus speed and requires lower power by running the internal clock at half the speed of the data bus. The two factors combine to produce a total of four data transfers per internal clock cycle. Since the DDR2 internal clock runs at half the DDR external clock rate, DDR2 memory operating at the same external data bus clock rate as DDR results in DDR2 being able to provide the same bandwidth but with better latency. Alter ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PlayStation 3

The PlayStation 3 (PS3) is a home video game console developed and marketed by Sony Computer Entertainment (SCE). It is the successor to the PlayStation 2, and both are part of the PlayStation brand of consoles. The PS3 was first released on November 11, 2006, in Japan, followed by November 17 in North America and March 23, 2007, in Europe and Australasia. It competed primarily with Microsoft's Xbox 360 and Nintendo's Wii as part of the seventh generation of video game consoles. The PlayStation 3 was built around the custom-designed Cell Broadband Engine processor, co-developed with IBM and Toshiba. SCE president Ken Kutaragi envisioned the console as a supercomputer for the living room, capable of handling complex multimedia tasks. It was the first console to use the Blu-ray disc as its primary storage medium, the first to be equipped with an HDMI port, and the first capable of outputting games in 1080p (Full HD) resolution. It also launched alongside the PlayStation Network ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Rambus Incorporated

Rambus Inc. is an American technology company that designs, develops and licenses chip interface technologies and architectures that are used in digital electronics products. The company, founded in 1990, is well known for inventing RDRAM and for its intellectual property-based litigation following the introduction of DDR-SDRAM memory. History Rambus was founded in March 1990 by electrical and computer engineers, Mike Farmwald and Mark Horowitz. The company's early investors included premier venture capital and investment banking firms such as Kleiner Perkins Caufield and Byers, Merrill Lynch, Mohr Davidow Ventures, and Goldman Sachs. Rambus was incorporated and founded as California company in 1990 and then re-incorporated in the state of Delaware before the company went public in 1997 on the NASDAQ stock exchange under the symbol RMBS. In the 1990s, Rambus was a high-speed interface technology development and marketing company that invented 600 MHz inter ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR3

Double Data Rate 3 Synchronous Dynamic Random-Access Memory (DDR3 SDRAM) is a type of synchronous dynamic random-access memory (SDRAM) with a high Bandwidth (computing), bandwidth ("double data rate") interface, and has been in use since 2007. It is the higher-speed successor to DDR SDRAM, DDR and DDR2 SDRAM, DDR2 and predecessor to DDR4 SDRAM, DDR4 synchronous dynamic random-access memory (SDRAM) chips. DDR3 SDRAM is neither Forward compatibility, forward nor Backward compatibility, backward compatible with any earlier type of random-access memory (RAM) because of different signaling voltages, timings, and other factors. DDR3 is a DRAM interface specification. The actual DRAM arrays that store the data are similar to earlier types, with similar performance. The primary benefit of DDR3 SDRAM over its immediate predecessor DDR2 SDRAM, is its ability to transfer data at twice the rate (eight times the speed of its internal memory arrays), enabling higher bandwidth or peak data ra ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

XDR DRAM

XDR DRAM (extreme data rate dynamic random-access memory) is a high-performance dynamic random-access memory interface. It is based on and succeeds RDRAM. Competing technologies include DDR2 and GDDR4. Overview XDR was designed to be effective in small, high-bandwidth consumer systems, high-performance memory applications, and high-end GPUs. It eliminates the unusually high latency problems that plagued early forms of RDRAM. Also, XDR DRAM has heavy emphasis on per-pin bandwidth, which can benefit further cost control on PCB production. This is because fewer lanes are needed for the same amount of bandwidth. Rambus owns the rights to the technology. XDR is used by Sony in the PlayStation 3 console. Technical specifications Performance * Initial clock rate at 400 MHz. * (ODR): Eight bits per clock cycle per lane. * Each chip provides 8, 16, or 32 programmable lanes, providing up to 230.4 Gbit/s (28.8 GB/s) at 900 MHz (7.2 GHz effective). Feat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |