|

ZSeries

IBM Z is a family name used by IBM for all of its z/Architecture mainframe computers. In July 2017, with another generation of products, the official family was changed to IBM Z from IBM z Systems; the IBM Z family will soon include the newest model, the IBM z17, as well as the z16, z15, z14, and z13 (released under the IBM z Systems/IBM System z names), the IBM zEnterprise models (in common use the zEC12 and z196), the IBM System z10 models (in common use the z10 EC), the IBM System z9 models (in common use the z9EC) and ''IBM eServer zSeries'' models (in common use refers only to the z900 and z990 generations of mainframe). Architecture The ''zSeries,'' ''zEnterprise,'' ''System z'' and ''IBM Z'' families were named for their availability – ''z'' stands for zero downtime. The systems are built with spare components capable of hot failovers to ensure continuous operations. The IBM Z family maintains full backward compatibility. In effect, current systems are the direc ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM Z15 Mainframe

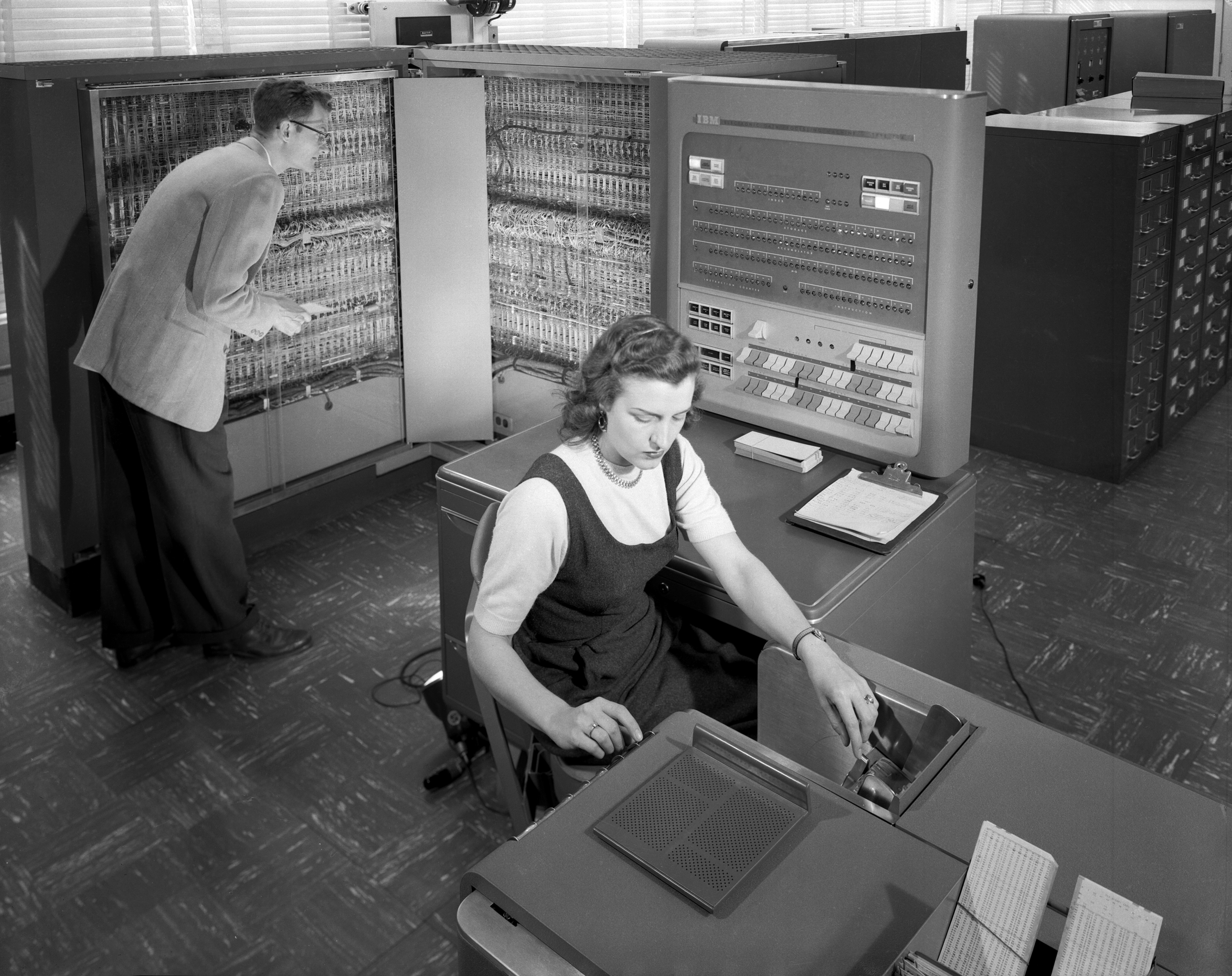

International Business Machines Corporation (using the trademark IBM), nicknamed Big Blue, is an American Multinational corporation, multinational technology company headquartered in Armonk, New York, and present in over 175 countries. It is a publicly traded company and one of the 30 companies in the Dow Jones Industrial Average. IBM is the largest industrial research organization in the world, with 19 research facilities across a dozen countries; for 29 consecutive years, from 1993 to 2021, it held the record for most annual U.S. patents generated by a business. IBM was founded in 1911 as the Computing-Tabulating-Recording Company (CTR), a holding company of manufacturers of record-keeping and measuring systems. It was renamed "International Business Machines" in 1924 and soon became the leading manufacturer of Tabulating machine, punch-card tabulating systems. During the 1960s and 1970s, the IBM mainframe, exemplified by the IBM System/360, System/360 and its successors, wa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Common Criteria

The Common Criteria for Information Technology Security Evaluation (referred to as Common Criteria or CC) is an international standard (International Organization for Standardization, ISO/International Electrotechnical Commission, IEC 15408) for computer security certification. It is currently in version 3.1 revision 5. Common Criteria is a framework in which computer system users can ''specify'' their security ''functional'' and ''assurance'' requirements (SFRs and SARs, respectively) in a Security Target (ST), and may be taken from Protection Profiles (PPs). Vendors can then ''implement'' or make claims about the security attributes of their products, and testing laboratories can ''evaluate'' the products to determine if they actually meet the claims. In other words, Common Criteria provides assurance that the process of specification, implementation and evaluation of a computer security product has been conducted in a rigorous and standard and repeatable manner at a level that is ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Coupling Facility

In IBM System/390 and IBM Z mainframe computers, a Coupling Facility or CF is a piece of computer hardware or virtual machine that coordinates multiple processors. A Parallel Sysplex relies on one or more Coupling Facilities (CFs). A coupling facility is a mainframe processor (runs in an own LPAR, with dedicated physical CP, defined through Hardware Management Console (HMC)), with memory and special channels (CF Links), and a specialized operating system called Coupling Facility Control Code (CFCC). It has no I/O devices, other than the CF links. The information in the CF resides entirely in memory as CFCC is not a virtual memory operating system. A CF typically has a large memory – of the order of several tens of gigabytes. The CF runs no application software. When originally introduced, the CFCC executed in a separate 9674 mainframe unit that was essentially a processor without I/O facilities other than the CF links. Later IBM enabled the use of an Internal Coupling Fac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ZIIP

In IBM System z9 and successor mainframes, the System z Integrated Information Processor (zIIP) is a special purpose processor. It was initially introduced to relieve the general mainframe central processors (CPs) of specific Db2 processing loads, but currently is used to offload other z/OS workloads as described below. The idea originated with previous special purpose processors, the zAAP, which offloads Java processing, and the IFL, which runs Linux and z/VM but not other IBM operating systems such as z/OS, DOS/VSE and TPF. A System z PU (processor unit) is "characterized" as one of these processor types, or as a CP (Central Processor), or SAP (System Assist Processor). These processors do not contain microcode or hardware features that accelerate their designated workloads. Instead, by relieving the general CP of particular workloads, they often lead to a higher workload throughput at reduced license fees. DB2 for z/OS V8 was the first application to exploit the zIIP, but ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Integrated Facility For Linux

The Integrated Facility for Linux (IFL) is an IBM mainframe and Power Systems processor dedicated to running the Linux operating system. On IBM Z and IBM LinuxONE machines, IFLs can be used with or without hypervisors such as z/VM and KVM. IFLs are one of three most common types of "specialty" IBM mainframe processors that give software vendors (and their customers) more granular control over software licensing and maintenance costs. (The other most common specialty processors are and ICFs). Microcode restricts IFLs to Linux workload by omitting some processor instructions not used by the Linux kernel (that other operating systems use), but the underlying processors are physically identical to general purpose processors (CPs). When IBM adds features and performance improvements to its mainframes' general purpose main processors (which can also run Linux), those features and improvements nearly always apply equally to IFLs. In fact, in recent IBM Z machines IFLs support sim ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Redundant Array Of Independent Memory

A redundant array of independent memory (RAIM) is a design feature found in certain computers' main random access memory. RAIM utilizes additional memory modules and striping algorithms to protect against the failure of any particular module and keep the memory system operating continuously. RAIM is similar in concept to a redundant array of independent disks (RAID), which protects against the failure of a disk drive, but in the case of memory it supports several DRAM device chipkills and entire memory channel failures. RAIM is much more robust than parity checking and ECC memory technologies which cannot protect against many varieties of memory failures. On July 22, 2010, IBM International Business Machines Corporation (using the trademark IBM), nicknamed Big Blue, is an American Multinational corporation, multinational technology company headquartered in Armonk, New York, and present in over 175 countries. It is ... introduced the first high end computer server featu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM Z14

The z14 is a microprocessor made by IBM for their z14 mainframe computers, announced on July 17, 2017. Manufactured at GlobalFoundries' East Fishkill, New York fabrication plant. IBM stated that it is the world's fastest microprocessor by clock rate at 5.2 GHz, with a 10% increased performance per core and 30% for the whole chip compared to its predecessor the z13. Description The Processor Unit chip (PU chip) has an area of 696 mm2 (25.3 × 27.5 mm) and consists of 6.1 billion transistors. It is fabricated using GlobalFoundries' 14 nm FinFET silicon on insulator fabrication process, using 17 layers of metal and supporting speeds of 5.2 GHz, which is higher than its predecessor, the z13. The PU chip has 10 cores but can have 7–10 cores (or "processor units" in IBM's parlance) enabled depending on configuration. The z14 cores support two-way simultaneous multithreading for more applications than previously available. The PU chip is packaged in a sing ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM Z15

The z15 is a microprocessor made by IBM for their z15 mainframe computers, announced on September 12, 2019. Description The processor unit chip (PU chip) has 12 cores. The z15 cores support two-way simultaneous multithreading. The cores implement the CISC z/Architecture with a superscalar, out-of-order pipeline. New in z15 is an on-chip nest accelerator unit, shared by all cores, to accelerate compression. The cache (e.g. level 3) is doubled from the previous generation z14, while the "L4 cache increased from 672MB to 960MB, or +43%" with the new add-on chip system controller (SC) SCM. Both it and all levels of cache in the main processor from level 1 use eDRAM Embedded DRAM (eDRAM) is dynamic random-access memory (DRAM) integrated on the same die or multi-chip module (MCM) of an application-specific integrated circuit (ASIC) or microprocessor. eDRAM's cost-per-bit is higher when compared to equivale ..., instead of the traditionally used SRAM. "A five-CPC drawer sys ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Neural Net

In machine learning, a neural network (also artificial neural network or neural net, abbreviated ANN or NN) is a computational model inspired by the structure and functions of biological neural networks. A neural network consists of connected units or nodes called ''artificial neurons'', which loosely model the neurons in the brain. Artificial neuron models that mimic biological neurons more closely have also been recently investigated and shown to significantly improve performance. These are connected by ''edges'', which model the synapses in the brain. Each artificial neuron receives signals from connected neurons, then processes them and sends a signal to other connected neurons. The "signal" is a real number, and the output of each neuron is computed by some non-linear function of the sum of its inputs, called the '' activation function''. The strength of the signal at each connection is determined by a ''weight'', which adjusts during the learning process. Typically, neuro ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM Telum

Telum is a microprocessor made by IBM for the IBM z16 series mainframe computers. The processor was announced at the Hot Chips 2021 conference on 23 August 2021. Telum is IBM's first processor that contains on-chip acceleration for artificial intelligence inferencing while a transaction is taking place. Description The chip contains 8 processor cores with a deep superscalar out-of-order pipeline, running with more than 5 GHz clock frequency which is optimized for the demands of heterogenous enterprise-class workloads (e.g: finance, security sensitive applications, applications requiring extreme reliability). The cache and chip-interconnection infrastructure provides 32 MB cache per core and can scale to 32 Telum chips. The cache design has been described as "revolutionary" in 2021, by creating a system where the L2 cache of one core can be used as virtual L3 and L4 caches for another core. The Telum processor can either be water cooled or air cooled, but water cooling is req ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

OpenCAPI

Coherent Accelerator Processor Interface (CAPI), is a high-speed processor expansion bus standard for use in large data center computers, initially designed to be layered on top of PCI Express, for directly connecting central processing units (CPUs) to external accelerators like graphics processing units (GPUs), ASICs, FPGAs or fast storage. It offers low latency, high speed, direct memory access connectivity between devices of different instruction set architectures. History The performance scaling traditionally associated with Moore's Law—dating back to 1965—began to taper off around 2004, as both Intel's Prescott architecture and IBM's Cell processor pushed toward a 4 GHz operating frequency. Here both projects ran into a thermal scaling wall, whereby heat extraction problems associated with further increases in operating frequency largely outweighed gains from shorter cycle times. Over the decade that followed, few commercial CPU products exceeded 4 GHz, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Data Processing Unit

A data processing unit (DPU) is a programmable Processor (computing), computer processor that tightly integrates a general-purpose CPU with Network interface controller, network interface hardware. Sometimes they are called "IPUs" (for "infrastructure processing unit") or "SmartNICs". They can be used in place of traditional Network interface controller, NICs to relieve the main CPU of complex networking responsibilities and other "infrastructural" duties; although their features vary, they may be used to perform Encryption, encryption/decryption, serve as a firewall (computing), firewall, handle TCP/IP, process HTTP requests, or even function as a hypervisor or Disk array controller, storage controller. These devices can be attractive to cloud computing providers whose servers might otherwise spend a significant amount of CPU time on these tasks, cutting into the cycles they can provide to guests. AI Factory, AI factories are an emerging use case for DPUs. In these environments, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |