|

Stack Register

A stack register is a computer central processor register whose purpose is to keep track of a call stack. On an accumulator-based architecture machine, this may be a dedicated register. On a machine with multiple general-purpose registers, it may be a register that is reserved by convention, such as on the IBM System/360 through z/Architecture architecture and RISC architectures, or it may be a register that procedure call and return instructions are hardwired to use, such as on the PDP-11, VAX, and Intel x86 architectures. Some designs such as the Data General Eclipse had no dedicated register, but used a reserved hardware memory address for this function. Machines before the late 1960s—such as the PDP-8 and HP 2100—did not have compilers which supported recursion. Their subroutine instructions typically would save the current location in the jump address, and then set the program counter to the ''next'' address. While this is simpler than maintaining a stack, si ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

|

Processor Register

A processor register is a quickly accessible location available to a computer's processor. Registers usually consist of a small amount of fast storage, although some registers have specific hardware functions, and may be read-only or write-only. In computer architecture, registers are typically addressed by mechanisms other than main memory, but may in some cases be assigned a memory address e.g. DEC PDP-10, ICT 1900. Almost all computers, whether load/store architecture or not, load items of data from a larger memory into registers where they are used for arithmetic operations, bitwise operations, and other operations, and are manipulated or tested by machine instructions. Manipulated items are then often stored back to main memory, either by the same instruction or by a subsequent one. Modern processors use either static or dynamic random-access memory (RAM) as main memory, with the latter usually accessed via one or more cache levels. Processor registers are normal ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

|

IA-32

IA-32 (short for "Intel Architecture, 32-bit", commonly called ''i386'') is the 32-bit version of the x86 instruction set architecture, designed by Intel and first implemented in the i386, 80386 microprocessor in 1985. IA-32 is the first incarnation of x86 that supports 32-bit computing; as a result, the "IA-32" term may be used as a Metonymy, metonym to refer to all x86 versions that support 32-bit computing. Within various programming language directives, IA-32 is still sometimes referred to as the "i386" architecture. In some other contexts, certain iterations of the IA-32 ISA are sometimes labelled ''i486'', ''i586'' and ''i686'', referring to the instruction supersets offered by the i486, 80486, the P5 (microarchitecture), P5 and the P6 (microarchitecture), P6 microarchitectures respectively. These updates offered numerous additions alongside the base IA-32 set including X87, floating-point capabilities and the MMX (instruction set), MMX extensions. Intel was historically ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

|

Control Flow

In computer science, control flow (or flow of control) is the order in which individual statements, instructions or function calls of an imperative program are executed or evaluated. The emphasis on explicit control flow distinguishes an ''imperative programming'' language from a ''declarative programming'' language. Within an imperative programming language, a ''control flow statement'' is a statement that results in a choice being made as to which of two or more paths to follow. For non-strict functional languages, functions and language constructs exist to achieve the same result, but they are usually not termed control flow statements. A set of statements is in turn generally structured as a block, which in addition to grouping, also defines a lexical scope. Interrupts and signals are low-level mechanisms that can alter the flow of control in a way similar to a subroutine, but usually occur as a response to some external stimulus or event (that can occur asynchr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

|

Simon & Schuster International Group

Simon & Schuster LLC (, ) is an American publishing house owned by Kohlberg Kravis Roberts since 2023. It was founded in New York City in 1924, by Richard L. Simon and M. Lincoln Schuster. Along with Penguin Random House, Hachette, HarperCollins and Macmillan Publishers, Simon & Schuster is considered one of the 'Big Five' English language publishers. , Simon & Schuster was the third largest publisher in the United States, publishing 2,000 titles annually under 35 different imprints. History Early years In 1924, Richard Simon's aunt, a crossword puzzle enthusiast, asked whether there was a book of ''New York World'' crossword puzzles, which were popular at the time. After discovering that none had been published, Simon and Max Schuster decided to launch a company to exploit the opportunity.Frederick Lewis Allen, ''Only Yesterday: An Informal History of the 1920s'', p. 165. . At the time, Simon was a piano salesman and Schuster was editor of an automotive trade magazine ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

|

Ellis Horwood Limited

Simon & Schuster LLC (, ) is an American publishing house owned by Kohlberg Kravis Roberts since 2023. It was founded in New York City in 1924, by Richard L. Simon and M. Lincoln Schuster. Along with Penguin Random House, Hachette Book Group USA, Hachette, HarperCollins and Macmillan Publishers, Simon & Schuster is considered one of the Big Five (publishers), 'Big Five' English language publishers. , Simon & Schuster was the third largest publisher in the United States, publishing 2,000 titles annually under 35 different Imprint (trade name), imprints. History Early years In 1924, Richard L. Simon, Richard Simon's aunt, a crossword puzzle enthusiast, asked whether there was a book of ''New York World'' crossword puzzles, which were popular at the time. After discovering that none had been published, Simon and M. Lincoln Schuster, Max Schuster decided to launch a company to exploit the opportunity.Frederick Lewis Allen, ''Only Yesterday: An Informal History of the 1920s'', p. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

|

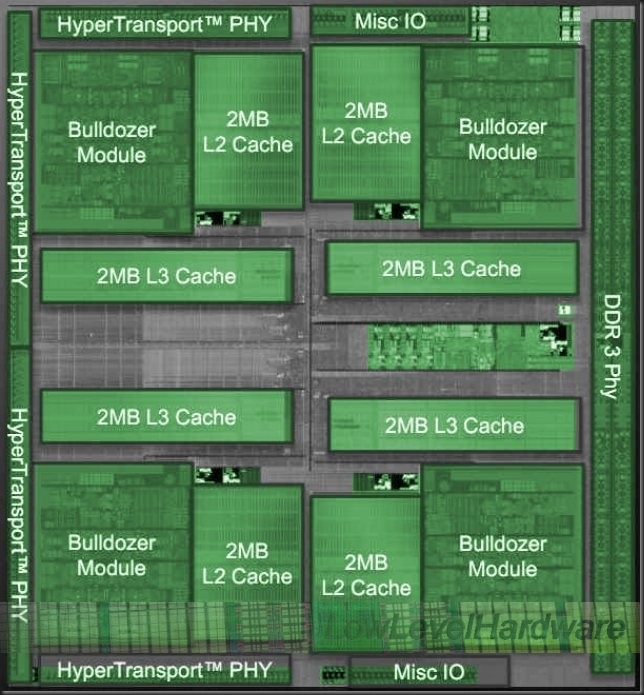

Bulldozer (microarchitecture)

The AMD Bulldozer Family 15h is a microprocessor microarchitecture for the FX and Opteron line of processors, developed by AMD for the desktop and server markets. Bulldozer is the codename for this family of microarchitectures. It was released on October 12, 2011, as the successor to the K10 microarchitecture. Bulldozer is designed from scratch, not a development of earlier processors. The core is specifically aimed at computing products with TDPs of 10 to 125 watts. AMD claims dramatic performance-per-watt efficiency improvements in high-performance computing (HPC) applications with Bulldozer cores. The ''Bulldozer'' cores support most of the instruction sets implemented by Intel processors ( Sandy Bridge) available at its introduction (including SSSE3, SSE4.1, SSE4.2, AES, CLMUL, and AVX) as well as new instruction sets proposed by AMD; ABM, XOP, FMA4 and F16C. Only Bulldozer GEN4 (Excavator) supports AVX2 instruction sets. Overview According to AMD, Bul ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

AMD K8

The AMD K8 Hammer, also code-named SledgeHammer, is a computer processor microarchitecture designed by AMD as the successor to the AMD K7 Athlon microarchitecture. The K8 was the first implementation of the AMD64 64-bit extension to the x86 instruction set architecture. Features Processors Processors based on the K8 core include: * Athlon 64 - first 64-bit consumer desktop * Athlon 64 X2 - first dual-core ('X2') desktop ** Athlon X2 - later model dual-core desktop with '64' omitted * Athlon 64 FX - enthusiast desktop (multipliers unlocked) * Sempron - low-end, low-cost desktop * Opteron - server market * Turion 64 - mobile computing market * Turion 64 X2 - dual-core mobile processor The K8 core is very similar to the K7. The most radical change is the integration of the AMD64 instructions and an on-chip memory controller. The memory controller drastically reduces memory latency and is largely responsible for most of the performance gains from K7 to K8. Nomenclat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

|

Pentium M

The Pentium M is a family of mobile 32-bit single-core x86 microprocessors (with the modified Intel P6 (microarchitecture), P6 microarchitecture) introduced in March 2003 and forming a part of the Intel Centrino#Carmel platform (2003), Carmel notebook platform under the then new Centrino brand. The ''Pentium M'' processors had a maximum thermal design power (TDP) of 5–27 W depending on the model, and were intended for use in laptops (thus the "M" suffix standing for ''mobile''). They evolved from the core of the last Pentium III–branded CPU by adding the front-side bus (FSB) interface of Pentium 4, an improved instruction decoding and issuing front end, improved branch predictor, branch prediction, SSE2 support, and a much larger cache. The Pentium M replaced the laptop version of the Pentium 4 (the ''Pentium 4-Mobile'', or ''P4-M''), which suffered from power consumption and heat problems. The first Pentium M–branded CPU, code-named Banias, was followed by Dothan. The Pent ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

Micro-op

In computer central processing units, micro-operations (also known as micro-ops or μops, historically also as micro-actions) are detailed low-level instructions used in some designs to implement complex machine instructions (sometimes termed macro-instructions in this context). Usually, micro-operations perform basic operations on data stored in one or more registers, including transferring data between registers or between registers and external buses of the central processing unit (CPU), and performing arithmetic or logical operations on registers. In a typical fetch-decode-execute cycle, each step of a macro-instruction is decomposed during its execution so the CPU determines and steps through a series of micro-operations. The execution of micro-operations is performed under control of the CPU's control unit, which decides on their execution while performing various optimizations such as reordering, fusion and caching. Optimizations Various forms of μops have long bee ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

|

Arithmetic Logic Unit

In computing, an arithmetic logic unit (ALU) is a Combinational logic, combinational digital circuit that performs arithmetic and bitwise operations on integer binary numbers. This is in contrast to a floating-point unit (FPU), which operates on floating point numbers. It is a fundamental building block of many types of computing circuits, including the central processing unit (CPU) of computers, FPUs, and graphics processing units (GPUs). The inputs to an ALU are the data to be operated on, called operands, and a code indicating the operation to be performed (opcode); the ALU's output is the result of the performed operation. In many designs, the ALU also has status inputs or outputs, or both, which convey information about a previous operation or the current operation, respectively, between the ALU and external status registers. Signals An ALU has a variety of input and output net (electronics), nets, which are the electrical conductors used to convey Digital signal (electroni ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

Hardware Register

In digital electronics, especially computing, hardware registers are circuits typically composed of flip-flops, often with many characteristics similar to memory, such as: * Using an memory or port address to select a particular register in a manner similar to a memory address. * the ability to read or write one or multiple bits at a time. Their distinguishing characteristic, however, is that they also have special hardware-related functions beyond those of ordinary memory. So, depending on the point of view, hardware registers are like memory with additional hardware-related functions; or, memory circuits are like hardware registers that just store data. Hardware registers are used in the interface between software and peripherals. Software writes them to send information to the device, and reads them to get information from the device. Some hardware devices also include registers that are not visible to software, for their internal use. Depending on their complexity, moder ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

|

|

Intel 8086

The 8086 (also called iAPX 86) is a 16-bit computing, 16-bit microprocessor chip designed by Intel between early 1976 and June 8, 1978, when it was released. The Intel 8088, released July 1, 1979, is a slightly modified chip with an external 8-bit Bus (computing), data bus (allowing the use of cheaper and fewer supporting Integrated circuit, ICs),Fewer TTL buffers, latches, multiplexers (although the amount of TTL logic was not drastically reduced). It also permits the use of cheap 8080-family ICs, where the 8254 CTC, Intel 8255, 8255 PIO, and 8259 PIC were used in the IBM PC design. In addition, it makes PCB layout simpler and boards cheaper, as well as demanding fewer (1- or 4-bit wide) DRAM chips. and is notable as the processor used in the original IBM Personal Computer, IBM PC design. The 8086 gave rise to the x86 architecture, which eventually became Intel's most successful line of processors. On June 5, 2018, Intel released a limited-edition CPU celebrating the 40th anniv ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |