|

R5000

The R5000 is a 64-bit, bi-endian, superscalar, in-order execution 2-issue design microprocessor that implements the MIPS IV instruction set architecture (ISA) developed by Quantum Effect Design (QED) in 1996. The project was funded by MIPS Technologies, Inc (MTI), also the licensor. MTI then licensed the design to Integrated Device Technology (IDT), NEC, NKK, and Toshiba. The R5000 succeeded the QED R4600 and R4700 as their flagship high-end embedded microprocessor. IDT marketed its version of the R5000 as the 79RV5000, NEC as VR5000, NKK as the NR5000, and Toshiba as the TX5000. The R5000 was sold to PMC-Sierra when the company acquired QED. Derivatives of the R5000 are still in production today for embedded systems. Users Users of the R5000 in workstation and server computers were Silicon Graphics, Inc. (SGI) and Siemens-Nixdorf. SGI used the R5000 in their O2 and Indy low-end workstations. The R5000 was also used in embedded systems such as network routers and high-e ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SGI Indy

The Indy, code-named "Guinness", is a low-end multimedia workstation introduced on July 12, 1993 by Silicon Graphics Incorporated (SGI). SGI developed, manufactured, and marketed Indy as the lowest end of its product line, for computer-aided design (CAD), desktop publishing, and multimedia markets. It competed with Intel x86 computers, and with Windows and Macintosh, including using their files and running their applications via software emulation. It is the first computer to come standard with a video camera, called IndyCam. Indy was repackaged as a server model called Challenge S. Indy was discontinued on June 30, 1997, and support ended on December 31, 2011. Hardware The Indy is one of the smaller form factors of the time (41 cm × 36 cm × 8 cm). The sturdy, electric-blue colored "pizza box" chassis is comparable to a contemporary small desktop PC, and is intended to fit underneath a large CRT monitor. Designed for multimedia use, the Indy includes analog an ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SGI O2

The O2 is an entry-level Unix workstation introduced in 1996 by Silicon Graphics, Inc. (SGI) to replace their earlier Indy series. Like the Indy, the O2 uses a single MIPS microprocessor and was intended to be used mainly for multimedia. Its larger counterpart is the SGI Octane. The O2 was SGI's last attempt at a low-end workstation. Hardware System architecture Originally known as the "Moosehead" project, the O2 architecture features a proprietary high-bandwidth Unified Memory Architecture (UMA) to connect system components. A PCI bus is bridged onto the UMA with one slot available. It has a designer case and an internal modular construction. Two SCSI drives can be mounted on special caddies (one in the later R10000/R12000 models due to heat constraints) and an optional video capture / sound cassette mounted on the far left side. CPU The O2 came in two distinct CPU flavours: the low-end MIPS 180 to 350 MHz R5000- or RM7000-based units and the higher-end 150 to 400 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MIPS Architecture

MIPS (Microprocessor without Interlocked Pipelined Stages) is a family of reduced instruction set computer (RISC) instruction set architectures (ISA)Price, Charles (September 1995). ''MIPS IV Instruction Set'' (Revision 3.2), MIPS Technologies, Inc. developed by MIPS Computer Systems, now MIPS Technologies, based in the United States. There are multiple versions of MIPS, including MIPS I, II, III, IV, and V, as well as five releases of MIPS32/64 (for 32- and 64-bit implementations, respectively). The early MIPS architectures were 32-bit; 64-bit versions were developed later. As of April 2017, the current version of MIPS is MIPS32/64 Release 6. MIPS32/64 primarily differs from MIPS I–V by defining the privileged kernel mode System Control Coprocessor in addition to the user mode architecture. The MIPS architecture has several optional extensions: MIPS-3D, a simple set of floating-point SIMD instructions dedicated to 3D computer graphics; MDMX (MaDMaX), a more extensive i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Quantum Effect Design

Quantum Effect Devices, Inc. (QED), was a microprocessor design company incorporated in 1991 as Quantum Effect Design. It was based in Palo Alto, California. History The three founders, Tom Riordan, Earl Killian and Ray Kunita, were senior managers at MIPS Computer Systems Inc. They left MIPS at a time when the company was having a difficult time selling entire computer systems ( MIPS Magnum) instead of concentrating on building microprocessor chips which was MIPS' original mission. Soon after, SGI purchased MIPS. IDT was a major funder and customer for the initial QED design. Business The original product plan for QED was to build a MIPS microprocessor for a laptop computer. This was during the ACE initiative from Microsoft to support multiple RISC architectures for their new Windows NT operating system. System companies like DeskStation Technology and board companies like ShaBLAMM! Computer were building products in the hope that RISC-based personal computers would become ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cobalt Qube

The Cobalt Qube was a computer server appliance product line, meant to be web servers, developed by Cobalt Networks, Inc. (later purchased by Sun Microsystems) from 1998 to 2002 featuring a modified Red Hat Linux operating system and a proprietary GUI for server management. The original Qube systems were equipped with RM5230 or RM5231 microprocessors but later models used AMD K6-2 chips. NetBSD operating system has been ported to both the Cobalt Qube and RaQ. Models The Qube 2700 was the first product released by Cobalt Networks in 1998. Mark Orr, one of the Cobalt Networks' CEOs, came up with the cobalt color. The green LED in the front was Bill Scott's idea. The 2700 was not a development version number but came from the atomic number of cobalt, 27. The Qube 2700 used the RM5230 microprocessor. The next product was called the Qube 2800 before being sold. But, released in 2000, was eventually called the Qube 2, leaving the ''2800'' to designate the system type. The Qube 2 us ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cobalt RaQ

The Cobalt RaQ is a 1U rackmount server product line developed by Cobalt Networks, Inc. (later purchased by Sun Microsystems) featuring a modified Red Hat Linux operating system and a proprietary GUI for server management. The original RaQ systems were equipped with MIPS Technologies, MIPS RM5230 or RM5231 CPUs but later models used AMD K6-2 chips and then eventually Intel Pentium III CPUs for the final models. The Cobalt RaQ was the second product line produced by Cobalt Networks; the first was the Cobalt Qube. Server specifications Below is a list of Cobalt RaQ types, and their specs. Under an Original Equipment Manufacturer, OEM arrangement, RaQ 2 units were also produced by Seagate Technology, Seagate, in the form of the Seagate NasRaQ. There were variants of the RaQ 3 and RaQ 4 models known as the RaQ 3i or RaQ 4i (SCSI support, two Ethernet connectors, PCI connector), and the RaQ 4r (SCSI support, two Ethernet connectors, and Redundant array of independent disks, RAI ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

R4600

The R4600, code-named "Orion", is a microprocessor developed by Quantum Effect Design (QED) that implemented the MIPS III instruction set architecture (ISA). As QED was a design firm that did not fabricate or sell their designs, the R4600 was first licensed to Integrated Device Technology (IDT), and later to Toshiba and then JFE Holdings, NKK. These companies fabricated the microprocessor and marketed it. The R4600 was designed as a low-end workstation or high-end embedded microprocessor. Users included Silicon Graphics, Silicon Graphics, Inc. (SGI) for their SGI Indy, Indy workstation and DeskStation Technology for their Windows NT workstations. The R4600 was instrumental in making the Indy successful by providing good integer performance at a competitive price. In embedded systems, prominent users included Cisco Systems in their network routers and Canon Inc., Canon in their printers. History IDT was the first company to fabricate and ship the R4600. IDT produced first silicon i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

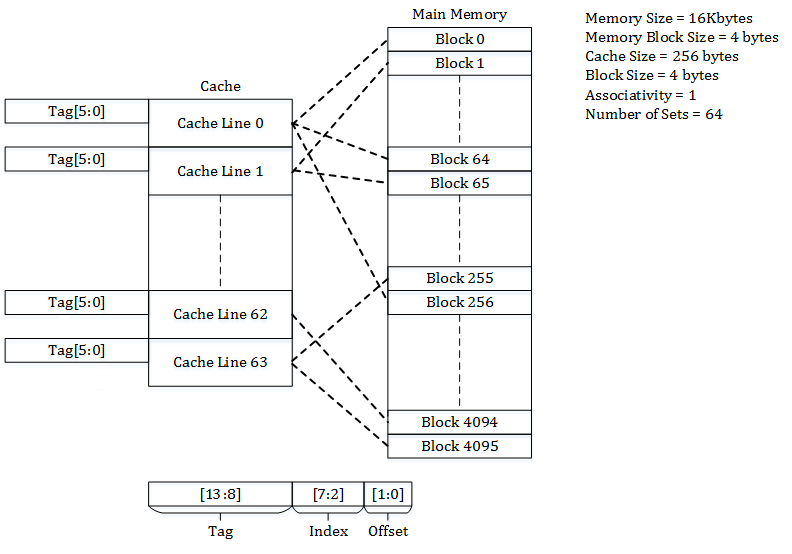

Set-associative

Cache placement policies are policies that determine where a particular memory block can be placed when it goes into a CPU cache. A block of memory cannot necessarily be placed at an arbitrary location in the cache; it may be restricted to a particular cache line or a set of cache lines by the cache's placement policy. There are three different policies available for placement of a memory block in the cache: direct-mapped, fully associative, and set-associative. Originally this space of cache organizations was described using the term "congruence mapping". Direct-mapped cache In a direct-mapped cache structure, the cache is organized into multiple sets with a single cache line per set. Based on the address of the memory block, it can only occupy a single cache line. The cache can be framed as a column matrix. To place a block in the cache * The set is determined by the index bits derived from the address of the memory block. * The memory block is placed in the set identif ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CPU Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (M ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Compiler

In computing, a compiler is a computer program that Translator (computing), translates computer code written in one programming language (the ''source'' language) into another language (the ''target'' language). The name "compiler" is primarily used for programs that translate source code from a high-level programming language to a lower level language, low-level programming language (e.g. assembly language, object code, or machine code) to create an executable program.Compilers: Principles, Techniques, and Tools by Alfred V. Aho, Ravi Sethi, Jeffrey D. Ullman - Second Edition, 2007 There are many different types of compilers which produce output in different useful forms. A ''cross-compiler'' produces code for a different Central processing unit, CPU or operating system than the one on which the cross-compiler itself runs. A ''bootstrap compiler'' is often a temporary compiler, used for compiling a more permanent or better optimised compiler for a language. Related software ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Branch Predictor

In computer architecture, a branch predictor is a digital circuit that tries to guess which way a branch (e.g., an if–then–else structure) will go before this is known definitively. The purpose of the branch predictor is to improve the flow in the instruction pipeline. Branch predictors play a critical role in achieving high performance in many modern pipelined microprocessor architectures. Two-way branching is usually implemented with a conditional jump instruction. A conditional jump can either be "taken" and jump to a different place in program memory, or it can be "not taken" and continue execution immediately after the conditional jump. It is not known for certain whether a conditional jump will be taken or not taken until the condition has been calculated and the conditional jump has passed the execution stage in the instruction pipeline (see fig. 1). Without branch prediction, the processor would have to wait until the conditional jump instruction has passed the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |