|

Ppc64le

ppc64 is an identifier commonly used within the Linux, GNU Compiler Collection (GCC) and LLVM open-source software communities to refer to the target architecture for applications optimized for 64-bit big-endian PowerPC and Power ISA processors. ppc64le is a pure little-endian mode that has been introduced with the POWER8 as the prime target for technologies provided by the OpenPOWER Foundation, aiming at enabling porting of the x86 Linux-based software with minimal effort. Details These two identifiers are frequently used when compiling source code to identify the target architecture. 64-bit Power and PowerPC processors are the following: * PowerPC 620 * RS64 – Apache, RS64-II Northstar, RS64-III Pulsar/IStar, and RS64-IV SStar * POWER3 and POWER3-II * POWER4 and POWER4+ * PowerPC 970, 970FX, 970MP and 970GX * POWER5 and POWER5+ * PPE in Cell BE, PowerXCell 8i and Xenon. * PWRficient * POWER6 and POWER6+ * POWER7 and POWER7+ * A2, A2I (used in the Blue ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

OpenPOWER Foundation

The OpenPOWER Foundation is a collaboration around Power ISA-based products initiated by IBM and announced as the "OpenPOWER Consortium" on August 6, 2013. IBM is opening up technology surrounding their Power Architecture offerings, such as processor specifications, firmware and software with a liberal license, and will be using a collaborative development model with their partners. The goal is to enable the server vendor ecosystem to build their own customized server, networking and storage hardware for future data centers and cloud computing. The governing body around the Power ISA instruction set is now the OpenPOWER Foundation: IBM allows its patents to be royalty-free for Compliant implementations. Processors based on IBM's IP can now be fabricated on any foundry and mixed with other hardware products of the integrator's choice. On August 20, 2019, IBM announced that the OpenPOWER Foundation would become part of the Linux Foundation. Openness IBM is using the word "o ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

POWER9

POWER9 is a family of superscalar, multithreading, multi-core microprocessors produced by IBM, based on the Power ISA. It was announced in August 2016. The POWER9-based processors are being manufactured using a 14 nm FinFET process, in 12- and 24-core versions, for scale out and scale up applications, and possibly other variations, since the POWER9 architecture is open for licensing and modification by the OpenPOWER Foundation members. Summit, the fourth fastest supercomputer in the world (based on the Top500 list as of June 2022), is based on POWER9, while also using Nvidia Tesla GPUs as accelerators. Design Core The POWER9 core comes in two variants, a four-way multithreaded one called ''SMT4'' and an eight-way one called ''SMT8''. The SMT4- and SMT8-cores are similar, in that they consist of a number of so-called ''slices'' fed by common schedulers. A slice is a rudimentary 64-bit single-threaded processing core with load store unit (LSU), integer unit (A ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

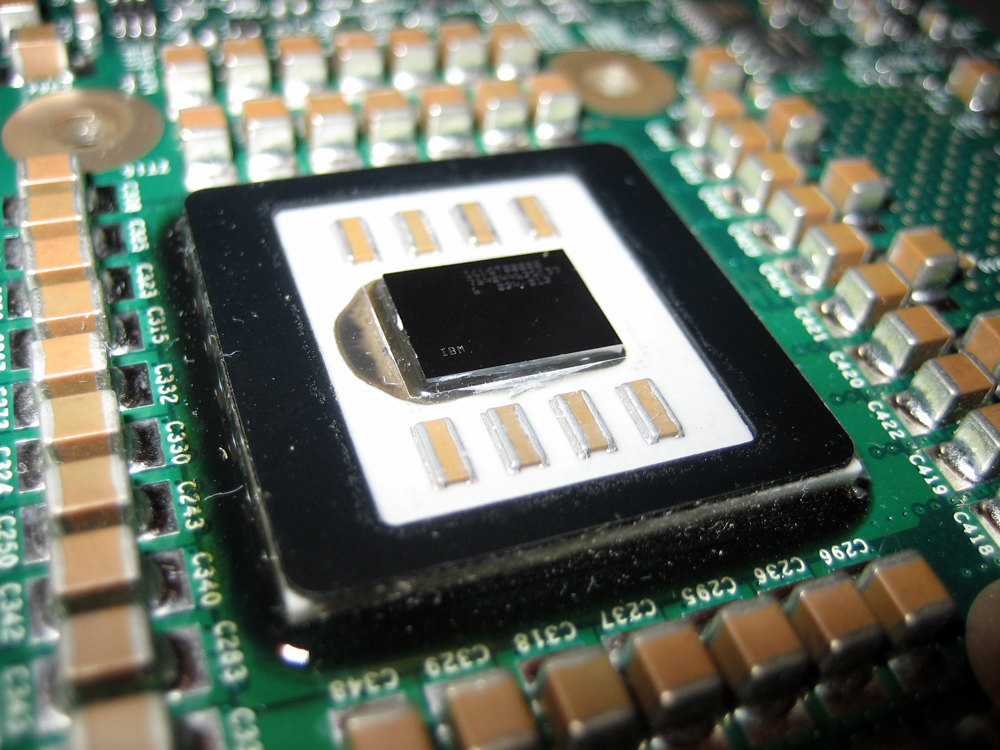

POWER4

The POWER4 is a microprocessor developed by International Business Machines (IBM) that implemented the 64-bit PowerPC and PowerPC AS instruction set architectures. Released in 2001, the POWER4 succeeded the POWER3 and RS64 microprocessors, enabling RS/6000 and eServer iSeries models of AS/400 computer servers to run on the same processor, as a step toward converging the two lines. The POWER4 was a multicore microprocessor, with two cores on a single die, the first non-embedded microprocessor to do so. POWER4 Chip was first commercially available multiprocessor chip.William Stallings, ''Computer Organization and Architecture'', Seventh Edition, -pp 44 The original POWER4 had a clock speed of 1.1 and 1.3 GHz, while an enhanced version, the POWER4+, reached a clock speed of 1.9 GHz. The PowerPC 970 is a derivative of the POWER4. Functional layout The POWER4 has a unified L2 cache, divided into three equal parts. Each has its own independent L2 controller which can ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Power10

Power10 is a superscalar, multithreading, multi-core microprocessor family, based on the open source Power ISA, and announced in August 2020 at the Hot Chips conference; systems with Power10 CPUs. Generally available from September 2021 in the IBM Power10 Enterprise E1080 server. The processor is designed to have 15 cores available, but a spare core will be included during manufacture to cost-effectively allow for yield issues. Power10-based processors will be manufactured by Samsung using a 7 nm process with 18 layers of metal and 18 billion transistors on a 602 mm2 silicon die. The main features of Power10 are higher performance per watt and better memory and I/O architectures, with a focus on artificial intelligence (AI) workloads. Design Each Power10 core has doubled up on most functional units compared to its predecessor POWER9. The core is eight-way multithreaded (SMT8) and has 48 KB instruction and 32 KB data L1 caches, a 2 MB large L2 c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerPC E6500

The PowerPC e6500 is a multithreaded 64-bit Power ISA-based microprocessor core from Freescale Semiconductor (now part of NXP). e6500 will power the entire range of QorIQ AMP Series system on a chip (SoC) processors which share the common naming scheme: "Txxxx". Hard samples, manufactured on a 28 nm process, available in early 2012 with full production later in 2012. Design It has a revised memory subsystem compared to the previous e5500 core with four cores combined into a CPU Cluster, sharing a large L2 cache and the e6500 cores supports up to eight CPU Clusters for very large multiprocessing implementations. The core is the first multithreaded core designed by Freescale and reintroduces an enhanced version of AltiVec to their products. The multithreading allows for two virtual cores per hard core and is organized as 2x2-way superscalar. One virtual core in an e6500 can often perform better than an entire e5500 core since Freescale essentially duplicated a lot of l ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerPC E5500 The PowerPC e5500 is a 64-bit Power ISA-based microprocessor core from Freescale Semiconductor. The core implements most of the core of the Power ISA v.2.06 with hypervisor support, but not AltiVec. It has a four issue, seven-stage out-of-order pipeline with a double precision FPU, three Integer units, 32/32 KB data and instruction L1 caches, 512 KB private L2 cache per core and up to 2 MB shared L3 cache. Speeds range up to 2.5 GHz, and the core is designed to be highly configurable via the CoreNet fabric and meet the specific needs of embedded applications with features like multi-core operation and interface for auxiliary application processing units (APU). Design The e5500 is based on the e500mc core and adds some new instructions introduced in the Power ISA 2.06 specification, namely some byte- and bit-level acceleration; Parity, Population count, Bit permute and Compare byte. The FPU is taken straight from the PowerPC e600 core, which is a classic fully pipeli ... [...More Info...] |

.png)