|

Placement (EDA)

Placement is an essential step in electronic design automation — the portion of the physical design flow that assigns exact locations for various circuit components within the chip's core area. An inferior placement assignment will not only affect the chip's performance but might also make it non-manufacturable by producing excessive wire-length, which is beyond available routing resources. Consequently, a placer must perform the assignment while optimizing a number of objectives to ensure that a circuit meets its performance demands. Together, the placement and routing steps of IC design are known as place and route. A placer takes a given synthesized circuit netlist together with a technology library and produces a valid placement layout. The layout is optimized according to the aforementioned objectives and ready for cell resizing and buffering — a step essential for timing and signal integrity satisfaction. Clock tree synthesis and Routing follow, completing the phys ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Electronic Design Automation

Electronic design automation (EDA), also referred to as electronic computer-aided design (ECAD), is a category of software tools for designing Electronics, electronic systems such as integrated circuits and printed circuit boards. The tools work together in a Design flow (EDA), design flow that chip designers use to design and analyze entire semiconductor chips. Since a modern semiconductor chip can have billions of components, EDA tools are essential for their design; this article in particular describes EDA specifically with respect to integrated circuits (ICs). History Early days The earliest electronic design automation is attributed to IBM with the documentation of its IBM 700/7000 series, 700 series computers in the 1950s. Prior to the development of EDA, integrated circuits were designed by hand and manually laid out. Some advanced shops used geometric software to generate tapes for a Gerber format, Gerber photoplotter, responsible for generating a monochromatic ex ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

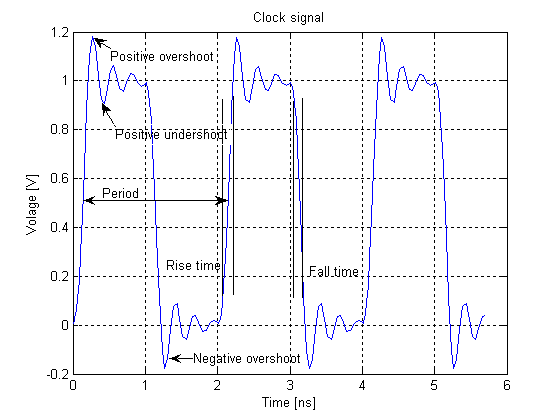

Clock Signal

In electronics and especially synchronous digital circuits, a clock signal (historically also known as ''logic beat'') is an electronic logic signal (voltage or current) which oscillates between a high and a low state at a constant frequency and is used like a metronome to synchronize actions of digital circuits. In a synchronous logic circuit, the most common type of digital circuit, the clock signal is applied to all storage devices, flip-flops and latches, and causes them all to change state simultaneously, preventing race conditions. A clock signal is produced by an electronic oscillator called a clock generator. The most common clock signal is in the form of a square wave with a 50% duty cycle. Circuits using the clock signal for synchronization may become active at either the rising edge, falling edge, or, in the case of double data rate, both in the rising and in the falling edges of the clock cycle. Digital circuits Most integrated circuits (ICs) of suffi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Place And Route

Place and route (also called PnR or P&R) is a stage in the design of printed circuit boards, integrated circuits, and field-programmable gate arrays. As implied by the name, it is composed of two steps, placement and routing. The first step, placement, involves deciding where to place all electronic components, circuitry, and logic elements in a generally limited amount of space. This is followed by routing, which decides the exact design of all the wires needed to connect the placed components. This step must implement all the desired connections while following the rules and limitations of the manufacturing process. Place and route is used in several contexts: * Printed circuit boards, during which components are graphically placed on the board and the wires drawn between them * Integrated circuits, during which a layout of a larger block of the circuit or the whole circuit is created from layouts of smaller sub-blocks * FPGAs, during which logic elements are placed and i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Floorplan (microelectronics)

In electronic design automation, a floorplan of an integrated circuit consists of a schematic arrangement of its major functional blocks on the chip area and the specification of high-level parameters such as the aspect ratio or core utilization. The design step in which floorplans are created is called floorplanning, an early stage in the Design flow (EDA), design flow for integrated circuit design. Various mathematical abstractions of this problem have been studied. Floorplanning design stage The floorplanning design stage consists of various steps with the aim of finding floorplans that allow a Timing closure, timing-clean routing and spread power consumption over the whole chip. *Chip Area Estimation: The dimensions and aspect ratio of the chip area are determined. The estimation considers the space required to place macros, standard cells and I/O ports while also leaving enough space for routing resources to enable a successful Place and route, place and route design fl ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Integrated Circuit Design

Integrated circuit design, semiconductor design, chip design or IC design, is a sub-field of electronics engineering, encompassing the particular Boolean logic, logic and circuit design techniques required to design integrated circuits (ICs). An IC consists of miniaturized electronic components built into an electrical network on a monolithic semiconductor substrate by photolithography. IC design can be divided into the broad categories of Digital data, digital and analog electronics, analog IC design. Digital IC design is to produce components such as microprocessors, FPGAs, memories (Random-access memory, RAM, Read-only memory, ROM, and flash memory, flash) and digital Application-specific integrated circuit, ASICs. Digital design focuses on logical correctness, maximizing circuit density, and placing circuits so that clock and timing signals are routed efficiently. Analog IC design also has specializations in power IC design and Radio frequency, RF IC design. Analog IC design ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Design Flow (EDA)

Design flows are the explicit combination of electronic design automation tools to accomplish the design of an integrated circuit. Moore's law has driven the entire IC implementation RTL to GDSII design flows from one which uses primarily stand-alone synthesis, placement, and routing algorithms to an integrated construction and analysis flows for design closure. The challenges of rising interconnect delay led to a new way of thinking about and integrating design closure tools. The RTL to GDSII flow underwent significant changes from 1980 through 2005. The continued scaling of CMOS technologies significantly changed the objectives of the various design steps. The lack of good predictors for delay has led to significant changes in recent design flows. New scaling challenges such as leakage power, variability, and reliability will continue to require significant changes to the design closure process in the future. Many factors describe what drove the design flow from a set ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Electronic Design Automation

Electronic design automation (EDA), also referred to as electronic computer-aided design (ECAD), is a category of software tools for designing Electronics, electronic systems such as integrated circuits and printed circuit boards. The tools work together in a Design flow (EDA), design flow that chip designers use to design and analyze entire semiconductor chips. Since a modern semiconductor chip can have billions of components, EDA tools are essential for their design; this article in particular describes EDA specifically with respect to integrated circuits (ICs). History Early days The earliest electronic design automation is attributed to IBM with the documentation of its IBM 700/7000 series, 700 series computers in the 1950s. Prior to the development of EDA, integrated circuits were designed by hand and manually laid out. Some advanced shops used geometric software to generate tapes for a Gerber format, Gerber photoplotter, responsible for generating a monochromatic ex ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Google Brain

Google Brain was a deep learning artificial intelligence research team that served as the sole AI branch of Google before being incorporated under the newer umbrella of Google AI, a research division at Google dedicated to artificial intelligence. Formed in 2011, it combined open-ended machine learning research with information systems and large-scale computing resources. It created tools such as TensorFlow, which allow neural networks to be used by the public, and multiple internal AI research projects, and aimed to create research opportunities in machine learning and natural language processing. It was merged into former Google sister company DeepMind to form Google DeepMind in April 2023. History The Google Brain project began in 2011 as a part-time research collaboration between Google fellow Jeff Dean (computer scientist), Jeff Dean and Google Researcher Greg Corrado. Google Brain started as a Google X project and became so successful that it was graduated back to Google: As ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IEEE Transactions On Computer-Aided Design Of Integrated Circuits And Systems

''IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems'' (sometimes abbreviated ''IEEE TCAD'' or ''IEEE Transactions on CAD'') is a monthly peer-reviewed scientific journal covering the design, analysis, and use of computer-aided design of integrated circuits and systems. It is published by the IEEE Circuits and Systems Society and the IEEE Council on Electronic Design Automation (Institute of Electrical and Electronics Engineers). The journal was established in 1982 and the editor-in-chief is Rajesh K. Gupta ( University of California at San Diego). According to the ''Journal Citation Reports'', the journal has a 2022 impact factor of 2.9. Past editors-in-chief *Rajesh K. Gupta (2018-2022) *Vijaykrishnan Narayanan (2014-2018) *Sachin Sapatnekar (2010-2014) See also *Electronic design automation Electronic design automation (EDA), also referred to as electronic computer-aided design (ECAD), is a category of software tools for designing Electronics, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Simulated Annealing

Simulated annealing (SA) is a probabilistic technique for approximating the global optimum of a given function. Specifically, it is a metaheuristic to approximate global optimization in a large search space for an optimization problem. For large numbers of local optima, SA can find the global optimum. It is often used when the search space is discrete (for example the traveling salesman problem, the boolean satisfiability problem, protein structure prediction, and job-shop scheduling). For problems where finding an approximate global optimum is more important than finding a precise local optimum in a fixed amount of time, simulated annealing may be preferable to exact algorithms such as gradient descent or branch and bound. The name of the algorithm comes from annealing in metallurgy, a technique involving heating and controlled cooling of a material to alter its physical properties. Both are attributes of the material that depend on their thermodynamic free energy ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Combinatorial Optimization

Combinatorial optimization is a subfield of mathematical optimization that consists of finding an optimal object from a finite set of objects, where the set of feasible solutions is discrete or can be reduced to a discrete set. Typical combinatorial optimization problems are the travelling salesman problem ("TSP"), the minimum spanning tree problem ("MST"), and the knapsack problem. In many such problems, such as the ones previously mentioned, exhaustive search is not tractable, and so specialized algorithms that quickly rule out large parts of the search space or approximation algorithms must be resorted to instead. Combinatorial optimization is related to operations research, algorithm theory, and computational complexity theory. It has important applications in several fields, including artificial intelligence, machine learning, auction theory, software engineering, VLSI, applied mathematics and theoretical computer science. Applications Basic applications of combina ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Field-programmable Gate Array

A field-programmable gate array (FPGA) is a type of configurable integrated circuit that can be repeatedly programmed after manufacturing. FPGAs are a subset of logic devices referred to as programmable logic devices (PLDs). They consist of an array of programmable logic device, programmable logic block, logic blocks with a connecting grid, that can be configured "in the field" to interconnect with other logic blocks to perform various digital functions. FPGAs are often used in limited (low) quantity production of custom-made products, and in research and development, where the higher cost of individual FPGAs is not as important, and where creating and manufacturing a custom circuit would not be feasible. Other applications for FPGAs include the telecommunications, automotive, aerospace, and industrial sectors, which benefit from their flexibility, high signal processing speed, and parallel processing abilities. A FPGA configuration is generally written using a hardware descr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |