|

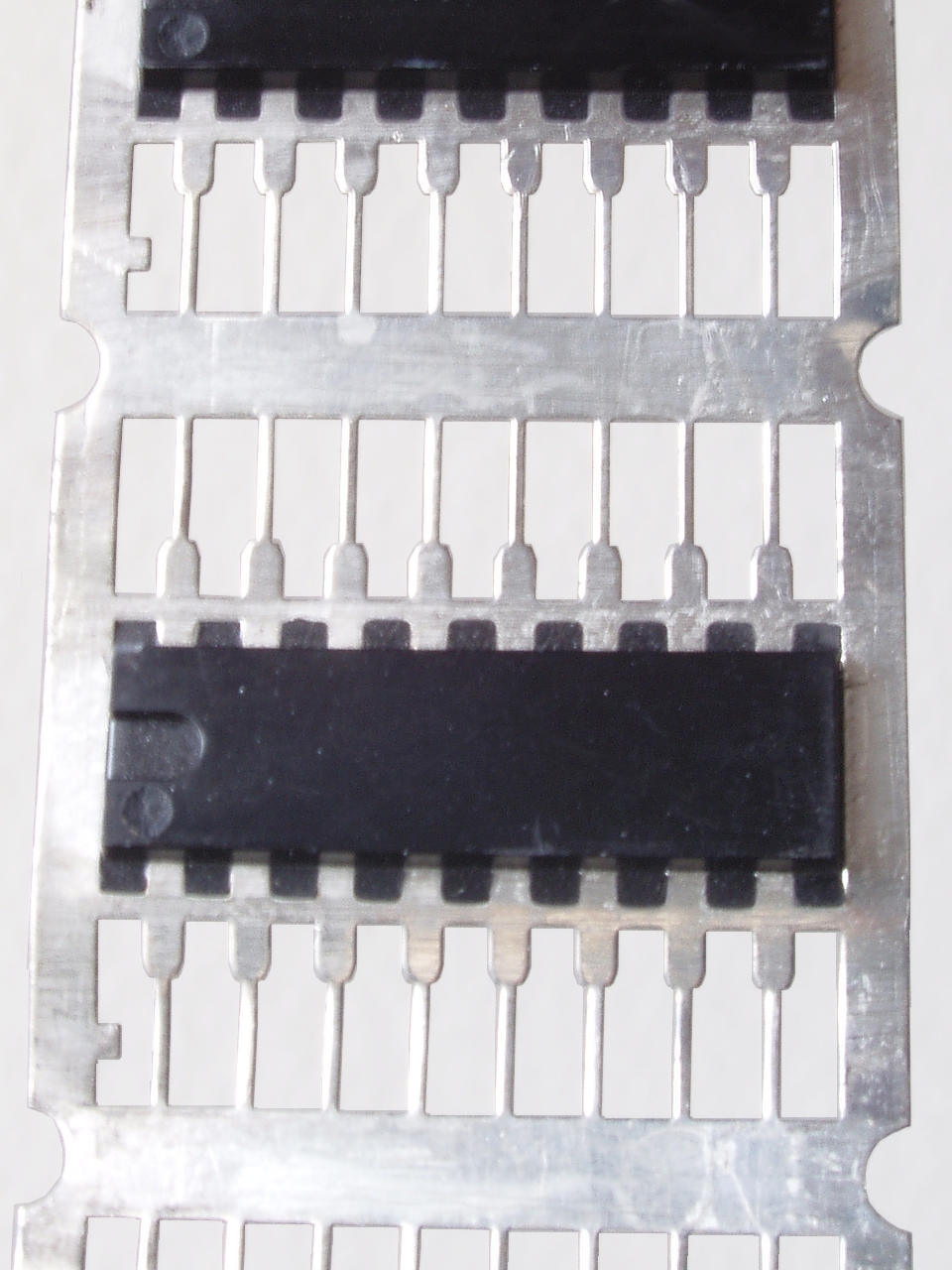

Lead Frame

A lead frame (pronounced ) is a metal structure inside a chip package that carries signals from the die to the outside, used in DIP, QFP and other packages where connections to the chip are made on its edges. The lead frame consists of a central die pad, where the die is placed, surrounded by leads, metal conductors leading away from the die to the outside world. The end of each lead closest to the die ends in a bond pad. Small bond wires connect the die to each bond pad. Mechanical connections fix all these parts into a rigid structure, which makes the whole lead frame easy to handle automatically. Manufacturing Lead frames are manufactured by removing material from a flat plate of copper, copper-alloy, or iron-nickel alloy like alloy 42. Two processes used for this are etching (suitable for high density of leads), or stamping (suitable for low density of leads). The mechanical bending process can be applied after both techniques. A lead frame has two sections: a die paddle, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Integrated Circuit Packaging

Integrated circuit packaging is the final stage of fabrication (semiconductor), semiconductor device fabrication, in which the die (integrated circuit), die is encapsulated in a supporting case that prevents physical damage and corrosion. The case, known as a "semiconductor package, package", supports the electrical contacts which connect the device to a circuit board. The packaging stage is followed by testing of the integrated circuit. Design considerations Electrical The current-carrying traces that run out of the die, through the package, and into the printed circuit board (PCB) have very different electrical properties compared to on-chip signals. They require special design techniques and need much more electric power than signals confined to the chip itself. Therefore, it is important that the materials used as electrical contacts exhibit characteristics like low resistance, low capacitance and low inductance. Both the structure and materials must prioritize sign ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

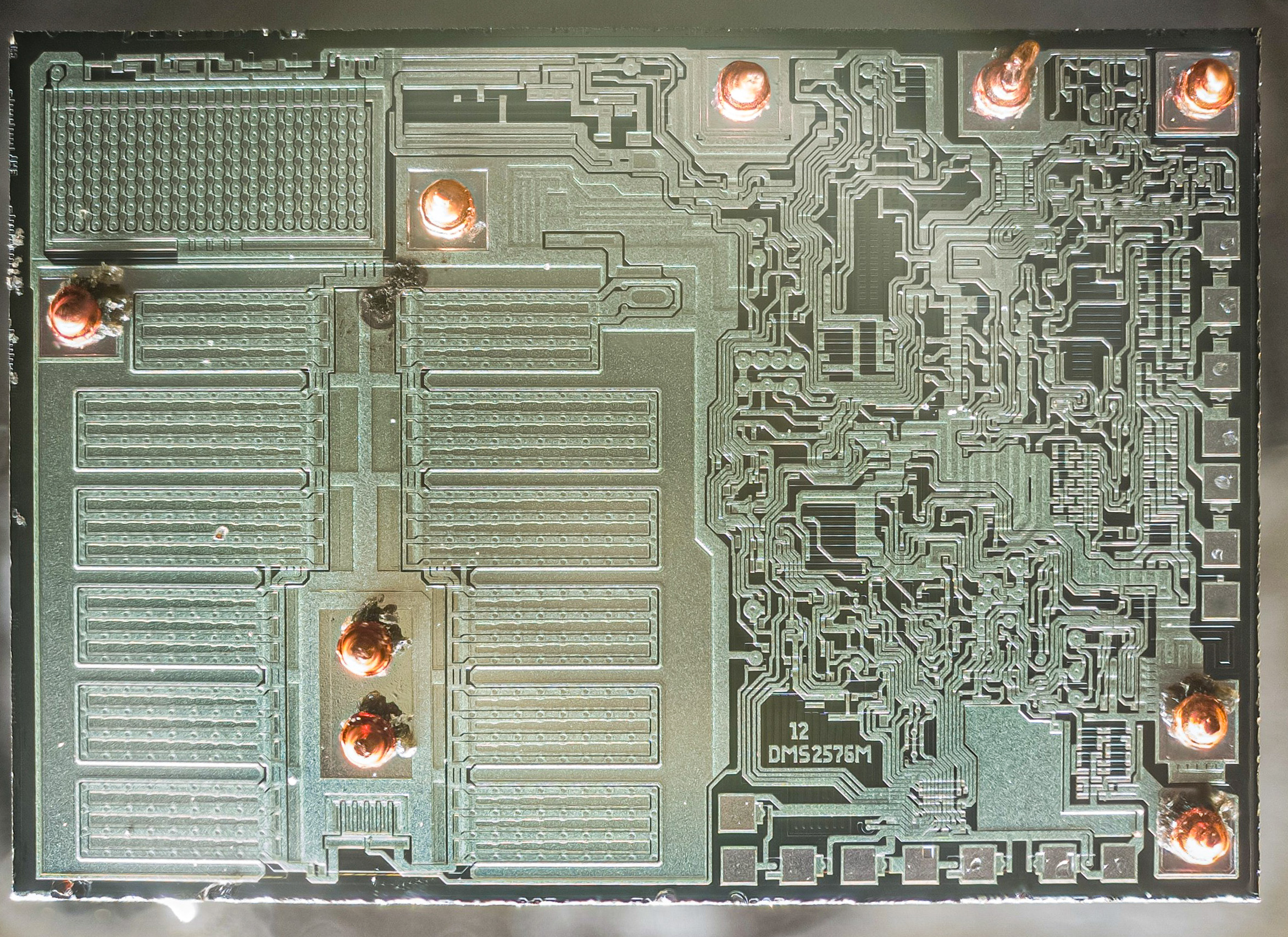

Die (integrated Circuit)

A die, in the context of integrated circuits, is a small block of semiconducting material on which a given functional circuit is Semiconductor fabrication, fabricated. Typically, integrated circuits are produced in large batches on a single wafer (electronics), wafer of electronic-grade Monocrystalline silicon, silicon (EGS) or other semiconductor (such as Gallium arsenide, GaAs) through processes such as photolithography. The wafer is cut (wafer dicing, diced) into many pieces, each containing one copy of the circuit. Each of these pieces is called a die. There are three commonly used plural forms: ''dice'', ''dies,'' and ''die''. To simplify handling and integration onto a printed circuit board, most dies are integrated circuit packaging, packaged in List of electronic component packaging types, various forms. Manufacturing process Most dies are composed of silicon and used for integrated circuits. The process begins with the production of Single crystal, monocrystalline sili ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

TQFP Leadframe

A quad flat package (QFP) is a surface-mount technology, surface-mounted integrated circuit integrated circuit packaging, package with "gull wing" leads extending from each of the four sides. Socketing such packages is rare and through-hole mounting is not possible. Versions ranging from 32 to 304 pins with a pin pitch, pitch ranging from 0.4 to 1.0 mm are common. Other special variants include low-profile QFP (LQFP) and thin QFP (TQFP). The first QFPs were introduced in Japan in 1977 in order to provide more pins on a small package to allow a greater number of digits on electronic calculators. It soon spread to other consumer electronics in that country. The QPF only became common in Europe and United States during the early nineties. It is often mixed with through-hole, hole mounted, and sometimes DIP socket, socketed, components on the same printed circuit board (PCB). A package related to QFP is plastic leaded chip carrier (PLCC) which is similar but has pins with larg ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

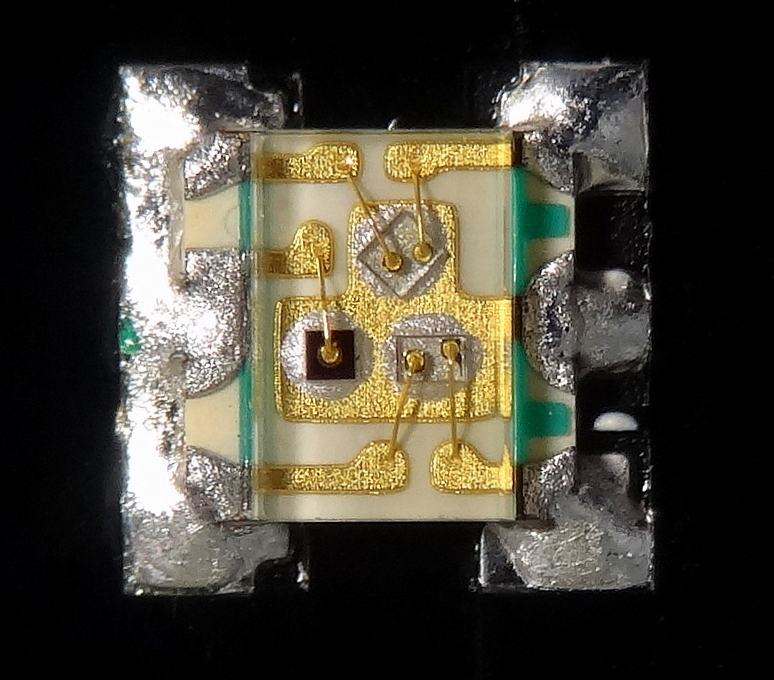

Wire Bonding

Wire bonding is a method of making interconnections between an integrated circuit (IC) or other semiconductor device and its packaging during semiconductor device fabrication. Wire bonding can also be used to connect an IC to other electronics or to connect from one printed circuit board (PCB) to another, although these are less common. Wire bonding is generally considered the most cost-effective and flexible interconnect technology and is used to assemble the vast majority of semiconductor packages. Wire bonding can be used at frequencies above 100 GHz. [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Quad Flat No-leads Package

Flat no-leads packages such as quad-flat no-leads (QFN''and dual-flat no-leads (DFN) physically and electrically connect integrated circuits to printed circuit boards. Flat no-leads, also known as micro leadframe (MLF) and SON (small-outline no leads), is a surface-mount technology, one of several package technologies that connect ICs to the ''surfaces'' of PCBs without through-holes. Flat no-lead is a near chip scale plastic encapsulated package made with a planar copper lead frame substrate. Perimeter lands on the package bottom provide electrical connections to the PCB. Flat no-lead packages usually, but not always, include an exposed thermally conductive pad to improve heat transfer out of the IC (into the PCB). Heat transfer can be further facilitated by metal vias in the thermal pad. The QFN package is similar to the quad-flat package (QFP), and a ball grid array (BGA). Flat no-lead cross-section The figure shows the cross section of a flat no-lead package with ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Quad Flat Package

A quad flat package (QFP) is a surface-mounted integrated circuit package with "gull wing" leads extending from each of the four sides. Socketing such packages is rare and through-hole mounting is not possible. Versions ranging from 32 to 304 pins with a pitch ranging from 0.4 to 1.0 mm are common. Other special variants include low-profile QFP (LQFP) and thin QFP (TQFP). The first QFPs were introduced in Japan in 1977 in order to provide more pins on a small package to allow a greater number of digits on electronic calculators. It soon spread to other consumer electronics in that country. The QPF only became common in Europe and United States during the early nineties. It is often mixed with hole mounted, and sometimes socketed, components on the same printed circuit board (PCB). A package related to QFP is plastic leaded chip carrier (PLCC) which is similar but has pins with larger pitch, 1.27 mm (or 1/20 inch), curved up underneath a thicker body to simpli ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Dual In-line Package

In microelectronics, a dual in-line package (DIP or DIL) is an Semiconductor package, electronic component package with a rectangular housing and two parallel rows of electrical connecting pins. The package may be through-hole technology, through-hole mounted to a printed circuit board (PCB) or inserted in a socket. The dual-inline format was invented by Don Forbes, Rex Rice and Bryant Rogers at Fairchild Semiconductor, Fairchild R&D in 1964, when the restricted number of leads available on circular transistor-style packages became a limitation in the use of integrated circuits. Increasingly complex circuits required more signal and power supply leads (as observed in Rent's rule); eventually microprocessors and similar complex devices required more leads than could be put on a DIP package, leading to development of higher-density chip carriers. Furthermore, square and rectangular packages made it easier to route printed-circuit traces beneath the packages. A DIP is usually refer ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Chip Carrier

In electronics, a chip carrier is one of several kinds of surface-mount technology packages for integrated circuits (commonly called "chips"). Connections are made on all four edges of a square package; compared to the internal cavity for mounting the integrated circuit, the package overall size is large.Kenneth Jackson, Wolfgang Schroter, (ed), ''Handbook of Semiconductor Technology Volume 2'', Wiley VCH, 2000, , page 627 Types Chip carriers may have either J-shaped metal leads for connections by solder or by a socket, or may be lead-less with metal pads for connections. If the leads extend beyond the package, the preferred description is " flat pack". Chip carriers can be smaller than dual in-line packages and since they use all four edges of the package they can have a larger pin count. Chip carriers may be made of ceramic or plastic. Some forms of chip carrier package are standardized in dimensions and registered with trade industry associations such as JEDEC. Other forms a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |