|

Ice Lake (microprocessor)

Ice Lake is Intel's List of Intel codenames, codename for the 10th generation Intel Core mobile and 3rd generation Xeon Scalable server processors based on the Sunny Cove (microarchitecture), Sunny Cove microarchitecture. Ice Lake represents an Architecture step in Intel's process–architecture–optimization model. Produced on the second generation of Intel's 10 nanometer, 10 nm process, 10 nm+, Ice Lake is Intel's second microarchitecture to be manufactured on the 10 nm process, following the limited launch of Cannon Lake (microarchitecture), Cannon Lake in 2018. However, Intel altered their naming scheme in 2020 for the 10 nm process. In this new naming scheme, Ice Lake's manufacturing process is called simply 10 nm, without any appended pluses. Ice Lake CPUs are sold together with the 14 nm Comet Lake CPUs as Intel's "10th Generation Core" product family. There are no Ice Lake desktop or high-power mobile processors; Comet Lake fulfills this ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

10 Nm Process

In semiconductor fabrication, the International Technology Roadmap for Semiconductors (ITRS) defines the "10 nanometer process" as the MOSFET technology node following the "14 nm" node. Since at least 1997, "process nodes" have been named purely on a marketing basis, and have no relation to the dimensions on the integrated circuit; neither gate length, metal pitch or gate pitch on a "10nm" device is ten nanometers. For example, GlobalFoundries' " 7 nm" processes are dimensionally similar to Intel's "10 nm" process. TSMC and Samsung's "10 nm" processes are somewhere between Intel's "14 nm" and "10 nm" processes in transistor density. The transistor density (number of transistors per square millimetre) is more important than transistor size, since smaller transistors no longer necessarily mean improved performance, or an increase in the number of transistors. All production "10 nm" processes are based on FinFET (fin field-effect transistor) tec ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Process–architecture–optimization Model

Process–architecture–optimization is a development model for central processing units (CPUs) that Intel adopted in 2016. Under this three-phase (three-year) model, every microprocessor A microprocessor is a computer processor (computing), processor for which the data processing logic and control is included on a single integrated circuit (IC), or a small number of ICs. The microprocessor contains the arithmetic, logic, a ... die shrink is followed by a microarchitecture change and then by one or more optimizations. It replaced the two-phase (two-year) tick–tock model that Intel adopted in 2006. The tick–tock model was no longer economically sustainable, according to Intel, because production of ever smaller dies becomes ever more costly. [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Machine Learning

Machine learning (ML) is a field of study in artificial intelligence concerned with the development and study of Computational statistics, statistical algorithms that can learn from data and generalise to unseen data, and thus perform Task (computing), tasks without explicit Machine code, instructions. Within a subdiscipline in machine learning, advances in the field of deep learning have allowed Neural network (machine learning), neural networks, a class of statistical algorithms, to surpass many previous machine learning approaches in performance. ML finds application in many fields, including natural language processing, computer vision, speech recognition, email filtering, agriculture, and medicine. The application of ML to business problems is known as predictive analytics. Statistics and mathematical optimisation (mathematical programming) methods comprise the foundations of machine learning. Data mining is a related field of study, focusing on exploratory data analysi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Deep Learning Boost

{{Third-party, date=March 2021 Intel's Deep Learning Boost (DL Boost) is a marketing name for instruction set architecture (ISA) features on the x86-64 designed to improve performance on deep learning tasks such as training and inference. Features DL Boost consists of two sets of features: * AVX-512 VNNI, 4VNNIW, or AVX-VNNI: fast multiply-accumulation mainly for convolutional neural networks. * AVX-512 BF16: lower-precision bfloat16 floating-point numbers for generally faster computation. Operations provided include conversion to/from float32 and dot product. DL Boost features were introduced in the Cascade Lake architecture. A TensorFlow-based benchmark run on the Google Cloud Platform Google Cloud Platform (GCP) is a suite of cloud computing services offered by Google that provides a series of modular cloud services including computing, Computer data storage, data storage, Data analysis, data analytics, and machine learnin ... Compute Engine shows improved performa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Secure Hash Algorithms

The Secure Hash Algorithms are a family of cryptographic hash functions published by the National Institute of Standards and Technology (NIST) as a U.S. Federal Information Processing Standard (FIPS), including: * SHA-0: A retronym applied to the original version of the 160-bit hash function published in 1993 under the name "SHA". It was withdrawn shortly after publication due to an undisclosed "significant flaw" and replaced by the slightly revised version SHA-1. *SHA-1: A 160-bit hash function which resembles the earlier MD5 algorithm. This was designed by the National Security Agency (NSA) to be part of the Digital Signature Algorithm. Cryptographic weaknesses were discovered in SHA-1, and the standard was no longer approved for most cryptographic uses after 2010. *SHA-2: A family of two similar hash functions, with different block sizes, known as ''SHA-256'' and ''SHA-512''. They differ in the word size; SHA-256 uses 32-bit words where SHA-512 uses 64-bit words. There are also ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Skylake (microarchitecture)

Skylake is Intel's codename for its sixth generation Core microprocessor family that was launched on August 5, 2015, succeeding the Broadwell microarchitecture. Skylake is a microarchitecture redesign using the same 14 nm manufacturing process technology as its predecessor, serving as a tock in Intel's tick–tock manufacturing and design model. According to Intel, the redesign brings greater CPU and GPU performance and reduced power consumption. Skylake CPUs share their microarchitecture with Kaby Lake, Coffee Lake, Whiskey Lake, and Comet Lake CPUs. Skylake is the last Intel platform on which Windows earlier than Windows 10 are officially supported by Microsoft, although enthusiast-created modifications are available that disabled the Windows Update check and allowed Windows 8.1 and earlier to continue to receive Windows Updates on this and later platforms. Some of the processors based on the Skylake microarchitecture are marketed as sixth-generation Core. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Instructions Per Clock

In computer architecture, instructions per cycle (IPC), commonly called instructions per clock, is one aspect of a processor's performance: the average number of instructions executed for each clock cycle. It is the multiplicative inverse of cycles per instruction. Explanation While early generations of CPUs carried out all the steps to execute an instruction sequentially, modern CPUs can do many things in parallel. As it is impossible to just keep doubling the speed of the clock, instruction pipelining and superscalar processor design have evolved so CPUs can use a variety of execution units in parallel - looking ahead through the incoming instructions in order to optimise them. This leads to the ''instructions per cycle completed'' being much higher than 1 and is responsible for much of the speed improvements in subsequent CPU generations. Calculation of IPC The calculation of IPC is done through running a set piece of code, calculating the number of machine-level instru ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

High Efficiency Video Coding

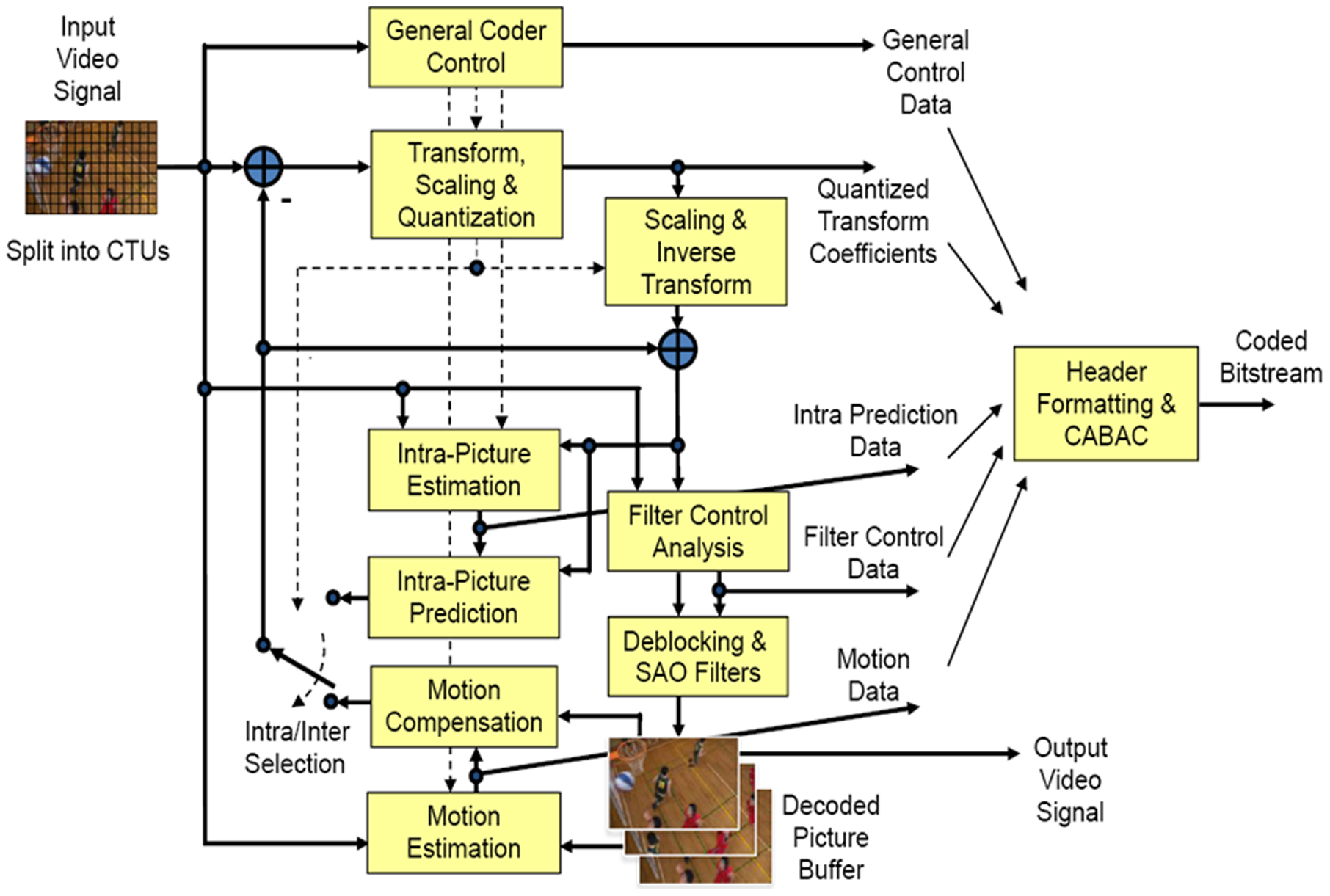

High Efficiency Video Coding (HEVC), also known as H.265 and MPEG-H Part 2, is a video compression standard designed as part of the MPEG-H project as a successor to the widely used Advanced Video Coding (AVC, H.264, or MPEG-4 Part 10). In comparison to AVC, HEVC offers from 25% to 50% better data compression at the same level of video quality, or substantially improved video quality at the same bit rate. It supports resolutions up to 8192×4320, including 8K UHD, and unlike the primarily 8-bit AVC, HEVC's higher fidelity Main 10 profile has been incorporated into nearly all supporting hardware. While AVC uses the integer discrete cosine transform (DCT) with 4×4 and 8×8 block sizes, HEVC uses both integer DCT and discrete sine transform (DST) with varied block sizes between 4×4 and 32×32. The High Efficiency Image Format (HEIF) is based on HEVC. Concept In most ways, HEVC is an extension of the concepts in H.264/MPEG-4 AVC. Both work by comparing different parts of a fra ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FLOPS

Floating point operations per second (FLOPS, flops or flop/s) is a measure of computer performance in computing, useful in fields of scientific computations that require floating-point calculations. For such cases, it is a more accurate measure than measuring instructions per second. Floating-point arithmetic Floating-point arithmetic is needed for very large or very small real numbers, or computations that require a large dynamic range. Floating-point representation is similar to scientific notation, except computers use base two (with rare exceptions), rather than base ten. The encoding scheme stores the sign, the exponent (in base two for Cray and VAX, base two or ten for IEEE floating point formats, and base 16 for IBM Floating Point Architecture) and the significand (number after the radix point). While several similar formats are in use, the most common is ANSI/IEEE Std. 754-1985. This standard defines the format for 32-bit numbers called ''single precision'', a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Haifa, Israel

Haifa ( ; , ; ) is the third-largest city in Israel—after Jerusalem and Tel Aviv—with a population of in . The city of Haifa forms part of the Haifa metropolitan area, the third-most populous metropolitan area in Israel. It is home to the Baháʼí Faith's Baháʼí World Centre, and is a UNESCO World Heritage Site and a destination for Baháʼí pilgrimage. Built on the slopes of Mount Carmel, the settlement has a history spanning more than 3,000 years. The earliest known settlement in the vicinity was Tell Abu Hawam, a small port city established in the Late Bronze Age (14th century BCE).Encyclopedia Judaica, ''Haifa'', Keter Publishing, Jerusalem, 1972, vol. 7, pp. 1134–1139 In the 3rd century CE, Haifa was known as a dye-making center. Over the millennia, the Haifa area has changed hands: being conquered and ruled by the Canaanites, Israelites, Phoenicians, Assyrians, Babylonians, Persians, Hasmoneans, Romans, Byzantines, Arabs, Crusaders, Ottomans, and the B ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Golden Cove

Golden Cove is a codename for a CPU microarchitecture developed by Intel and released in November 2021. It succeeds four microarchitectures: Sunny Cove, Skylake, Willow Cove, and Cypress Cove. It is fabricated using Intel's Intel 7 process node, previously referred to as 10nm Enhanced SuperFin (10ESF). The microarchitecture is used in the high-performance cores (P-core) of the 12th-generation Intel Core processors (codenamed " Alder Lake") and fourth-generation Xeon Scalable server processors (codenamed "Sapphire Rapids"). History and features Intel first unveiled Golden Cove during their Architecture Day 2020, with further details released at the same event in August 2021. Similar to Skylake, Golden Cove was described by Intel as a major update to the core microarchitecture, with Intel stating that it would "allow performance for the next decade of compute". Intel also described Golden Cove as the largest microarchitectural upgrade to the Core family in a decade, toutin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Xe

Intel Xe (stylized as Xe and pronounced as two separate letters, abbreviation for "exascale for everyone"), earlier known unofficially as Gen12, is a GPU architecture developed by Intel. Intel Xe includes a new instruction set architecture. The Xe GPU family consists of a series of microarchitectures, ranging from integrated/low power (Xe-LP), to enthusiast/high performance gaming (Xe-HPG), datacenter/high performance (Xe-HP) and high performance computing (Xe-HPC). History Intel's first attempt at a dedicated graphics card was the Intel740, released in February 1998. The Intel740 was considered unsuccessful due to its performance which was lower than market expectations, causing Intel to cease development on future discrete graphics products. However, its technology lived on in the Intel Extreme Graphics lineup. Intel made another attempt with the Larrabee architecture before canceling it in 2009; this time, the technology developed was used in the Xeon Phi, which was d ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |