|

GeForce 800M Series

The GeForce 800M series is a family of graphics processing units by Nvidia for laptop PCs. It consists of rebrands of mobile versions of the GeForce 700 series and some newer chips that are lower end compared to the rebrands. The GeForce 800 series name was originally planned to be used for both desktop and mobile chips based on the Maxwell (microarchitecture), Maxwell microarchitecture (GM-codenamed chips), named after the Scottish theoretical physicist James Clerk Maxwell, which was previously introduced into the GeForce 700 series in the GTX 750 and GTX 750 Ti, released on February 18, 2014. However, because mobile GPUs under the GeForce 800M series had already been released using the Kepler (microarchitecture), Kepler architecture, Nvidia decided to rename its GeForce 800 series desktop GPUs as the GeForce 900 series. The Maxwell (microarchitecture), Maxwell microarchitecture, the successor to Kepler (microarchitecture), Kepler microarchitecture, was the first Nvidia archit ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GeForce Newlogo

GeForce is a brand of List of Nvidia graphics processing units, graphics processing units (GPUs) designed by Nvidia and marketed for the performance market. As of the GeForce 50 series, there have been nineteen iterations of the design. In August 2017, Nvidia stated that "there are over 200 million GeForce gamers". The first GeForce products were discrete GPUs designed for add-on graphics boards, intended for the high-margin Gaming computer, PC gaming market, and later diversification of the product line covered all tiers of the PC graphics market, ranging from cost-sensitive GPUs integrated on motherboards to mainstream add-in retail boards. Most recently, GeForce technology has been introduced into Nvidia's line of embedded application processors, designed for electronic handhelds and mobile handsets. With respect to discrete GPUs, found in add-in graphics-boards, Nvidia's GeForce and AMD's Radeon GPUs are the only remaining competitors in the high-end market. GeForce GPUs a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

James Clerk Maxwell

James Clerk Maxwell (13 June 1831 – 5 November 1879) was a Scottish physicist and mathematician who was responsible for the classical theory of electromagnetic radiation, which was the first theory to describe electricity, magnetism and light as different manifestations of the same phenomenon. Maxwell's equations for electromagnetism achieved the Unification (physics)#Unification of magnetism, electricity, light and related radiation, second great unification in physics, where Unification (physics)#Unification of gravity and astronomy, the first one had been realised by Isaac Newton. Maxwell was also key in the creation of statistical mechanics. With the publication of "A Dynamical Theory of the Electromagnetic Field" in 1865, Maxwell demonstrated that electric force, electric and magnetic fields travel through space as waves moving at the speed of light. He proposed that light is an undulation in the same medium that is the cause of electric and magnetic phenomena. (Th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Bus (computing)

In computer architecture, a bus (historically also called a data highway or databus) is a communication system that transfers Data (computing), data between components inside a computer or between computers. It encompasses both Computer hardware, hardware (e.g., wires, optical fiber) and software, including communication protocols. At its core, a bus is a shared physical pathway, typically composed of wires, traces on a circuit board, or busbars, that allows multiple devices to communicate. To prevent conflicts and ensure orderly data exchange, buses rely on a communication protocol to manage which device can transmit data at a given time. Buses are categorized based on their role, such as system buses (also known as internal buses, internal data buses, or memory buses) connecting the Central processing unit, CPU and Computer memory, memory. Expansion buses, also called peripheral buses, extend the system to connect additional devices, including peripherals. Examples of widely ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nanometre

330px, Different lengths as in respect to the Molecule">molecular scale. The nanometre (international spelling as used by the International Bureau of Weights and Measures; SI symbol: nm), or nanometer (American spelling), is a unit of length in the International System of Units (SI), equal to one billionth ( short scale) or one thousand million (long scale) of a meter (0.000000001 m) and to 1000 picometres. One nanometre can be expressed in scientific notation as 1 × 10−9 m and as m. History The nanometre was formerly known as the "''millimicrometre''" – or, more commonly, the "''millimicron''" for short – since it is of a micrometer. It was often denoted by the symbol ''mμ'' or, more rarely, as ''μμ'' (however, ''μμ'' should refer to a ''millionth'' of a micron). Etymology The name combines the SI prefix '' nano-'' (from the Ancient Greek , ', "dwarf") with the parent unit name ''metre'' (from Greek , ', "unit of measurement"). ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Code Name

A code name, codename, call sign, or cryptonym is a code word or name used, sometimes clandestinely, to refer to another name, word, project, or person. Code names are often used for military purposes, or in espionage. They may also be used in industrial counter-espionage to protect secret projects and the like from business rivals, or to give names to projects whose marketing name has not yet been determined. Another reason for the use of names and phrases in the military is that they transmit with a lower level of cumulative errors over a walkie-talkie or radio link than actual names. Origins Achaemenid Empire The Achaemenid Empire under Darius I employed a network of spies called the King’s Eye or the King’s Ear. These agents operated under anonymity, and “King’s Eye” was not a specific person but rather a code name for the intelligence network that reported directly to the king. Punic Wars The Carthaginian general Hannibal Barca reportedly used coded re ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Render Output Unit

In computer graphics, the render output unit or raster operations pipeline (ROP) is a hardware component in modern graphics processing units (GPUs) and one of the final steps in the rendering process of modern graphics cards. The pixel pipelines take pixel (each pixel is a dimensionless point) and texel information and process it, via specific matrix and vector operations, into a final pixel or depth value; this process is called rasterization. Thus, ROPs control antialiasing, when more than one sample is merged into one pixel. The ROPs perform the transactions between the relevant buffers in the local memory – this includes writing or reading values, as well as blending them together. Dedicated antialiasing hardware used to perform hardware-based antialiasing methods like MSAA is contained in ROPs. All data rendered has to travel through the ROP in order to be written to the framebuffer, from there it can be transmitted to the display. Therefore, the ROP is where the GPU ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Texture Mapping Unit

In computer graphics, a texture mapping unit (TMU) is a component in modern graphics processing units (GPUs). They are able to rotate, resize, and distort a bitmap image to be placed onto an arbitrary plane of a given 3D model as a texture, in a process called texture mapping. In modern graphics cards it is implemented as a discrete stage in a graphics pipeline, whereas when first introduced it was implemented as a separate processor, e.g. as seen on the Voodoo2 graphics card. Background and history The TMU came about due to the compute demands of sampling and transforming a flat image (as the texture map) to the correct angle and perspective it would need to be in 3D space. The compute operation is a large matrix multiply, which CPUs of the time (early Pentiums for example) could not cope with at an acceptable level of performance. In 2013, TMUs are part of the shader pipeline and decoupled from the Render Output Pipelines (ROPs). For example, in AMD's Cypress GPU, each s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Unified Shader Model

In the field of 3D computer graphics, the unified shader model (known in Direct3D 10 as " Shader Model 4.0") refers to a form of shader hardware in a graphical processing unit (GPU) where all of the shader stages in the rendering pipeline A pipeline is a system of Pipe (fluid conveyance), pipes for long-distance transportation of a liquid or gas, typically to a market area for consumption. The latest data from 2014 gives a total of slightly less than of pipeline in 120 countries ... (geometry, vertex, pixel, etc.) have the same capabilities. They can all read textures and buffers, and they use instruction set architecture, instruction sets that are almost identical. History Earlier GPUs generally included two types of shader hardware, with the ''vertex shaders'' having considerably more instructions than the simpler ''pixel shaders''. This lowered the cost of implementation of the GPU as a whole, and allowed more shaders in total on a single unit. This was at the cost of mak ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CUDA

In computing, CUDA (Compute Unified Device Architecture) is a proprietary parallel computing platform and application programming interface (API) that allows software to use certain types of graphics processing units (GPUs) for accelerated general-purpose processing, an approach called general-purpose computing on GPUs. CUDA was created by Nvidia in 2006. When it was first introduced, the name was an acronym for ''Compute Unified Device Architecture'', but Nvidia later dropped the common use of the acronym and now rarely expands it. CUDA is a software layer that gives direct access to the GPU's virtual instruction set and parallel computational elements for the execution of compute kernels. In addition to drivers and runtime kernels, the CUDA platform includes compilers, libraries and developer tools to help programmers accelerate their applications. CUDA is designed to work with programming languages such as C, C++, Fortran, Python and Julia. This accessibility makes ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Warp Scheduler

Warp, warped or warping may refer to: Arts and entertainment Books and comics * WaRP Graphics, an alternative comics publisher * ''Warp'' (First Comics), comic book series published by First Comics based on the play ''Warp!'' * Warp (comics), a DC Comics supervillain * ''Warp'' (magazine), formerly the magazine and official organ of the New Zealand National Association for Science Music * Warp (record label), an independent UK record label ** Warp Films, a side project of Warp Records ** Warp 10: Influences, Classics, Remixes, a series of compilation albums issued by Warp Records in 1999 Albums * ''Warp'' (album), 1982 album by New Musik * ''Warp'', 2001 album by the Japanese band Judy and Mary * '' W.A.R.P.E.D.'', a 2005 album by Savatage guitarist Chris Caffery Songs * "Warp", 2009 single by The Bloody Beetroots * "Warped" (song), a song by the Red Hot Chili Peppers from their 1995 album ''One Hot Minute'' * "Warped", a song by Blackfoot from the 1980 album ''Tomcattin''' ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

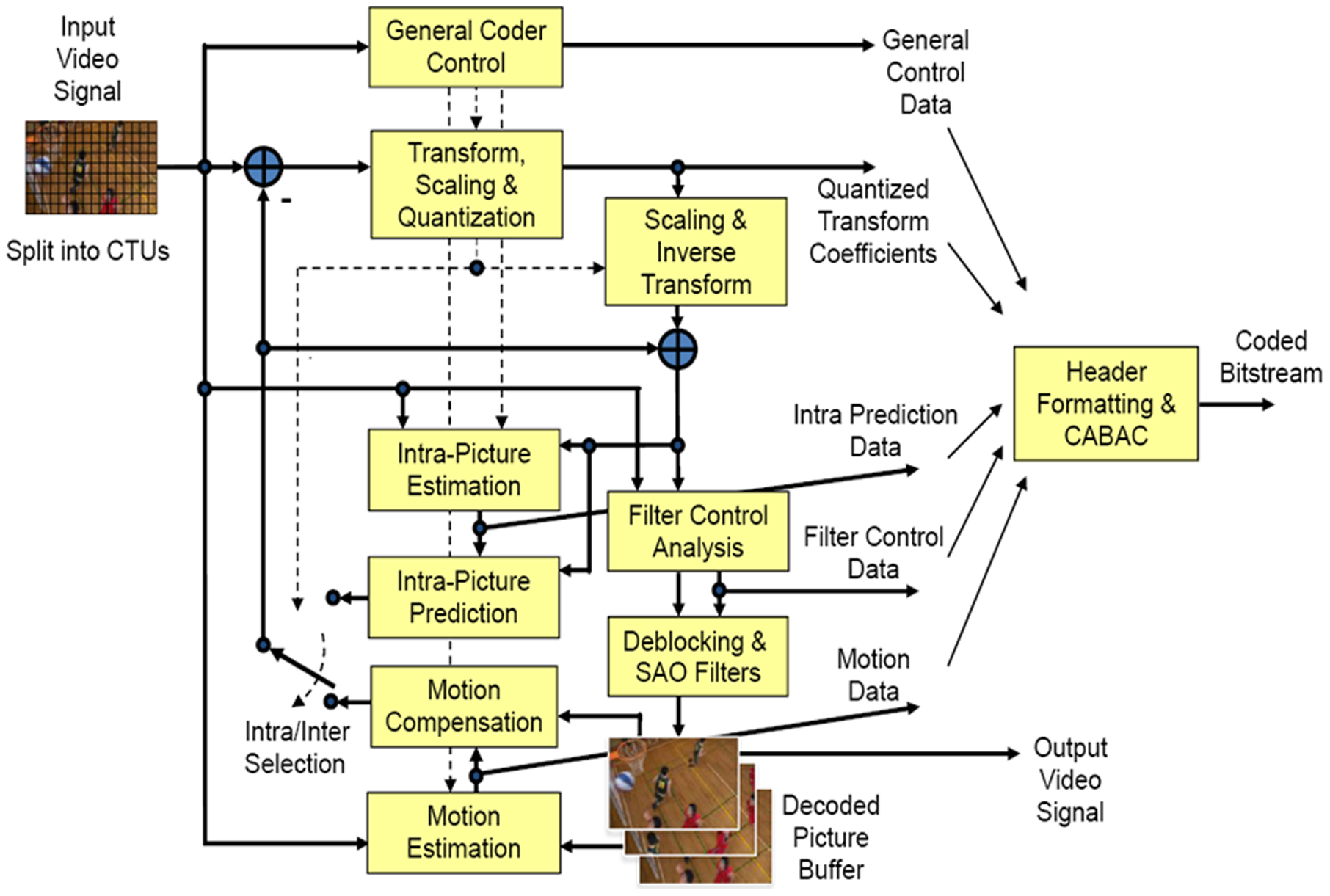

High Efficiency Video Coding

High Efficiency Video Coding (HEVC), also known as H.265 and MPEG-H Part 2, is a video compression standard designed as part of the MPEG-H project as a successor to the widely used Advanced Video Coding (AVC, H.264, or MPEG-4 Part 10). In comparison to AVC, HEVC offers from 25% to 50% better data compression at the same level of video quality, or substantially improved video quality at the same bit rate. It supports resolutions up to 8192×4320, including 8K UHD, and unlike the primarily 8-bit AVC, HEVC's higher fidelity Main 10 profile has been incorporated into nearly all supporting hardware. While AVC uses the integer discrete cosine transform (DCT) with 4×4 and 8×8 block sizes, HEVC uses both integer DCT and discrete sine transform (DST) with varied block sizes between 4×4 and 32×32. The High Efficiency Image Format (HEIF) is based on HEVC. Concept In most ways, HEVC is an extension of the concepts in H.264/MPEG-4 AVC. Both work by comparing different parts of a fra ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nvidia PureVideo

PureVideo is Nvidia's hardware SIP core that performs video decoding. PureVideo is integrated into some of the Nvidia GPUs, and it supports hardware decoding of multiple video codec standards: MPEG-2, VC-1, H.264, HEVC, and AV1. PureVideo occupies a considerable amount of a GPU's die area and should not be confused with Nvidia NVENC. In addition to video decoding on chip, PureVideo offers features such as edge enhancement, noise reduction, deinterlacing, dynamic contrast enhancement and color enhancement. Operating system support The PureVideo SIP core needs to be supported by the device driver, which provides one or more interfaces such as NVDEC, VDPAU, VAAPI or DXVA. One of these interfaces is then used by end-user software, for example VLC media player or GStreamer, to access the PureVideo hardware and make use of it. Nvidia's proprietary device driver is available for multiple operating systems and support for PureVideo has been added to it. Additionally, a free d ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |