|

Excavator Microarchitecture

AMD Excavator Family 15h is a microarchitecture developed by AMD to succeed Steamroller Family 15h for use in AMD APU processors and normal CPUs. On October 12, 2011, AMD revealed Excavator to be the code name for the fourth-generation Bulldozer-derived core. The Excavator-based APU for mainstream applications is called ''Carrizo'' and was released in 2015. The ''Carrizo'' APU is designed to be HSA 1.0 compliant. An Excavator-based APU and CPU variant named ''Toronto'' for server and enterprise markets was also produced. Excavator was the final revision of the "Bulldozer" family, with two new microarchitectures replacing Excavator a year later. Excavator was succeeded by the x86-64 Zen architecture in early 2017. Architecture Excavator added hardware support for new instructions such as AVX2, BMI2 and RDRAND. Excavator is designed using High Density (aka "Thin") Libraries normally used for GPUs to reduce electric energy consumption and die size, delivering a 30 percent increa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Graphics Processing Unit

A graphics processing unit (GPU) is a specialized electronic circuit designed for digital image processing and to accelerate computer graphics, being present either as a discrete video card or embedded on motherboards, mobile phones, personal computers, workstations, and game consoles. GPUs were later found to be useful for non-graphic calculations involving embarrassingly parallel problems due to their parallel structure. The ability of GPUs to rapidly perform vast numbers of calculations has led to their adoption in diverse fields including artificial intelligence (AI) where they excel at handling data-intensive and computationally demanding tasks. Other non-graphical uses include the training of neural networks and cryptocurrency mining. History 1970s Arcade system boards have used specialized graphics circuits since the 1970s. In early video game hardware, RAM for frame buffers was expensive, so video chips composited data together as the display was being scann ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ball Grid Array

A ball grid array (BGA) is a type of surface-mount packaging (a chip carrier) used for integrated circuits. BGA packages are used to permanently mount devices such as microprocessors. A BGA can provide more interconnection pins than can be put on a dual in-line or flat package. The whole bottom surface of the device can be used, instead of just the perimeter. The traces connecting the package's leads to the wires or balls which connect the die to package are also on average shorter than with a perimeter-only type, leading to better performance at high speeds. Soldering of BGA devices requires precise control and is usually done by automated processes such as in computer-controlled automatic reflow ovens. Description The BGA is descended from the pin grid array (PGA), which is a package with one face covered (or partly covered) with pins in a grid pattern which, in operation, conduct electrical signals between the integrated circuit and the printed circuit board (PCB) ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

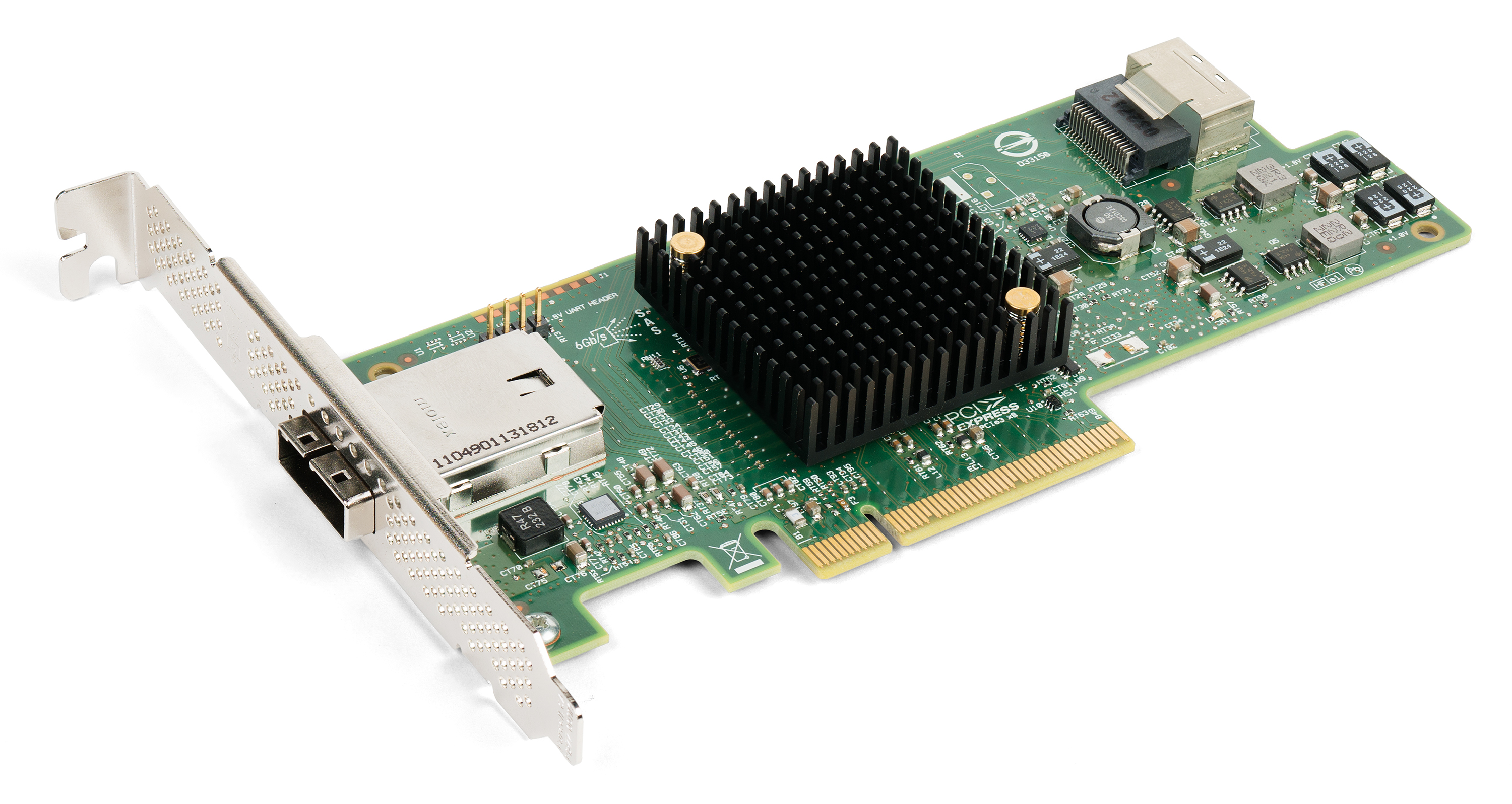

PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe, is a high-speed standard used to connect hardware components inside computers. It is designed to replace older expansion bus standards such as Peripheral Component Interconnect, PCI, PCI-X and Accelerated Graphics Port, AGP. Developed and maintained by the PCI-SIG (PCI Special Interest Group), PCIe is commonly used to connect graphics cards, sound cards, Wi-Fi and Ethernet adapters, and storage devices such as solid-state drives and hard disk drives. Compared to earlier standards, PCIe supports faster data transfer, uses fewer pins, takes up less space, and allows devices to be added or removed while the computer is running (hot swapping). It also includes better error detection and supports newer features like I/O virtualization for advanced computing needs. PCIe connections are made through "lanes," which are pairs of wires that send and receive data. Devices can use one or more lanes ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR3 SDRAM

Double Data Rate 3 Synchronous Dynamic Random-Access Memory (DDR3 SDRAM) is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth (" double data rate") interface, and has been in use since 2007. It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random-access memory (SDRAM) chips. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of random-access memory (RAM) because of different signaling voltages, timings, and other factors. DDR3 is a DRAM interface specification. The actual DRAM arrays that store the data are similar to earlier types, with similar performance. The primary benefit of DDR3 SDRAM over its immediate predecessor DDR2 SDRAM, is its ability to transfer data at twice the rate (eight times the speed of its internal memory arrays), enabling higher bandwidth or peak data rates. The DDR3 standard permits DRAM chip capacities of up to 8 gigabits (Gbit) (so 1 gigabyte by ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Instructions Per Cycle

In computer architecture, instructions per cycle (IPC), commonly called instructions per clock, is one aspect of a processor's performance: the average number of instructions executed for each clock cycle. It is the multiplicative inverse of cycles per instruction. Explanation While early generations of CPUs carried out all the steps to execute an instruction sequentially, modern CPUs can do many things in parallel. As it is impossible to just keep doubling the speed of the clock, instruction pipelining and superscalar processor design have evolved so CPUs can use a variety of execution units in parallel - looking ahead through the incoming instructions in order to optimise them. This leads to the ''instructions per cycle completed'' being much higher than 1 and is responsible for much of the speed improvements in subsequent CPU generations. Calculation of IPC The calculation of IPC is done through running a set piece of code, calculating the number of machine-level inst ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD Radeon Rx 200 Series

The Radeon 200 series is a series of graphics processors developed by AMD. These GPUs are manufactured on a 28 nm Gate-Last process through TSMC or Common Platform Alliance. Release The Rx 200 series was announced on September 25, 2013, at the AMD GPU14 Tech Day event. Non-disclosure agreements were lifted on October 15, except for the R9 290X, and pre-orders opened on October 3. Architecture * Graphics Core Next 3 (Volcanic Islands) is found on the R9 285 (Tonga Pro) branded products. * Graphics Core Next 2 (Sea Islands) is found on R7 260 (Bonaire), R7 260X (Bonaire XTX), R9 290 (Hawaii Pro), R9 290X (Hawaii XT), and R9 295X2 (Vesuvius) branded products. * Graphics Core Next 1 (Southern Islands) is found on R9 270, 270X, 280, 280X, R7 240, 250, 250X, 265, and R5 240 branded products. * TeraScale 2 (VLIW5) (Northern Islands or Evergreen) is found on R5 235X and below branded products. * OpenGL 4.x compliance requires supporting FP64 shaders. These are implemented by emula ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Graphics Core Next

Graphics Core Next (GCN) is the codename for a series of microarchitectures and an instruction set architecture that were developed by AMD for its GPUs as the successor to its TeraScale microarchitecture. The first product featuring GCN was launched on January 9, 2012. GCN is a reduced instruction set SIMD microarchitecture contrasting the very long instruction word SIMD architecture of TeraScale. GCN requires considerably more transistors than TeraScale, but offers advantages for general-purpose GPU (GPGPU) computation due to a simpler compiler. GCN graphics chips were fabricated with CMOS at 28 nm, and with FinFET at 14 nm (by Samsung Electronics and GlobalFoundries) and 7 nm (by TSMC), available on selected models in AMD's Radeon HD 7000, HD 8000, 200, 300, 400, 500 and Vega series of graphics cards, including the separately released Radeon VII. GCN was also used in the graphics portion of Accelerated Processing Units (APUs), including those in the PlayStation ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR4 SDRAM

Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) is a type of synchronous dynamic random-access memory with a high bandwidth (" double data rate") interface. Released to the market in 2014, it is a variant of dynamic random-access memory (DRAM), some of which have been in use since the early 1970s, and a higher-speed successor to the DDR2 and DDR3 technologies. DDR4 is not compatible with any earlier type of random-access memory (RAM) due to different signaling voltage and physical interface, besides other factors. DDR4 SDRAM was released to the public market in Q2 2014, focusing on ECC memory, while the non-ECC DDR4 modules became available in Q3 2014, accompanying the launch of Haswell-E processors that require DDR4 memory. Features The primary advantages of DDR4 over its predecessor, DDR3, include higher module density and lower voltage requirements, coupled with higher data rate transfer speeds. The DDR4 standard allows for DIMMs of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |