|

ETRAX CRIS

The ETRAX CRIS is a RISC Instruction set architecture, ISA and series of Central processing unit, CPUs designed and manufactured by Axis Communications for use in embedded systems since 1993. The name is an acronym of the chip's features: ''Ethernet, Token Ring, AXis - Code Reduced Instruction Set''. Token Ring support has been taken out from the latest chips as it has become obsolete. Types of chips The CGA-1 (Coax Gate Array) was the first microprocessor developed by Axis Communications. It contains IBM 3270 (coax) and IBM 5250 (Twinax) communications. The chip has a microcontroller and various I/O's such as serial and parallel. The CGA-1 chip was designed by Martin Gren and Staffan Göransson. ETRAX * In 1993, Axis developed the ETRAX-1 Ethernet Controller, which has 10 Mbit/s Ethernet and Token Ring controllers. * In 1995, Axis introduced the ETRAX-4 System on a chip, SoC which contains a Ethernet Controller, CPU, Memory Interface, SCSI controller, and parallel and seri ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

RISC

In electronics and computer science, a reduced instruction set computer (RISC) is a computer architecture designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set computer (CISC), a RISC computer might require more instructions (more code) in order to accomplish a task because the individual instructions perform simpler operations. The goal is to offset the need to process more instructions by increasing the speed of each instruction, in particular by implementing an instruction pipeline, which may be simpler to achieve given simpler instructions. The key operational concept of the RISC computer is that each instruction performs only one function (e.g. copy a value from memory to a register). The RISC computer usually has many (16 or 32) high-speed, general-purpose registers with a load–store architecture in which the code for the register-register instructions (for performing ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Wide SCSI

Parallel SCSI (formally, SCSI Parallel Interface, or SPI) is the earliest of the interface implementations in the SCSI family. SPI is a parallel bus; there is one set of electrical connections stretching from one end of the SCSI bus to the other. A SCSI device attaches to the bus but does not interrupt it. Both ends of the bus must be terminated. SCSI is a peer-to-peer peripheral interface. Every device attaches to the SCSI bus in a similar manner. Depending on the version, up to 8 or 16 devices can be attached to a single bus. There can be multiple hosts and multiple peripheral devices but there should be at least one host. The SCSI protocol defines communication from host to host, host to a peripheral device, and peripheral device to a peripheral device. The Symbios Logic 53C810 chip is an example of a PCI host interface that can act as a SCSI target. SCSI-1 and SCSI-2 have the option of parity bit error checking. Starting with SCSI-U160 (part of SCSI-3) all commands and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Advanced Encryption Standard

The Advanced Encryption Standard (AES), also known by its original name Rijndael (), is a specification for the encryption of electronic data established by the U.S. National Institute of Standards and Technology (NIST) in 2001. AES is a variant of the Rijndael block cipher developed by two Belgium, Belgian cryptographers, Joan Daemen and Vincent Rijmen, who submitted a proposal to NIST during the Advanced Encryption Standard process, AES selection process. Rijndael is a family of ciphers with different key size, key and Block size (cryptography), block sizes. For AES, NIST selected three members of the Rijndael family, each with a block size of 128 bits, but three different key lengths: 128, 192 and 256 bits. AES has been adopted by the Federal government of the United States, U.S. government. It supersedes the Data Encryption Standard (DES), which was published in 1977. The algorithm described by AES is a symmetric-key algorithm, meaning the same key is used for both encrypting ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Instructions Per Second

Instructions per second (IPS) is a measure of a computer's Central processing unit, processor speed. For complex instruction set computers (CISCs), different Machine code, instructions take different amounts of time, so the value measured depends on the instruction mix; even for comparing processors in the same family the IPS measurement can be problematic. Many reported IPS values have represented "peak" execution rates on artificial instruction sequences with few Subroutine, branches and no Resource contention, cache contention, whereas realistic workloads typically lead to significantly lower IPS values. Memory hierarchy also greatly affects processor performance, an issue barely considered in IPS calculations. Because of these problems, synthetic Benchmark (computing), benchmarks such as Dhrystone are now generally used to estimate computer performance in commonly used applications, and raw IPS has fallen into disuse. The term is commonly used in association with a metric pr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Comparison Of Synchronous And Asynchronous Signalling

Synchronous and asynchronous transmissions are two different methods of transmission synchronization. Synchronous transmissions are synchronized by an external clock, while asynchronous transmissions are synchronized by special signals along the transmission medium. The need for synchronization Whenever an electronic device transmits digital (and sometimes analogue) data to another, there must be a certain rhythm established between the two devices, i.e., the receiving device must have some way of, within the context of the fluctuating signal that it's receiving, determining where each unit of data begins and where it ends. Methods of synchronization There are two ways to synchronize the two ends of the communication. The synchronous signalling methods use two different signals. A pulse on one signal indicates when another bit of information is ready on the other signal. The asynchronous signalling methods use only one signal. The receiver uses transitions on that signal to f ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

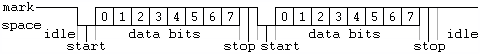

Asynchronous Serial Communication

Asynchronous serial communication is a form of serial communication in which the communicating endpoints' interfaces are not continuously synchronized by a common clock signal. Synchronization ( clock recovery) is done by data-embedded signal: the data stream contains synchronization information in a form of start and stop signals set before and after each payload transmission. The start signal prepares the receiver for arrival of data and the stop signal resets its state to enable triggering of a new sequence. A common kind of start-stop transmission is ASCII over RS-232, for example for use in teletypewriter operation. Origin Mechanical teleprinters using 5-bit codes (see Baudot code) typically used a stop period of 1.5 bit times.Dead link: 2015-Oct-03 Very early electromechanical teletypewriters (pre-1930) could require 2 stop bits to allow mechanical impression without buffering. Hardware which does not support fractional stop bits can communicate with a device that use ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Reduced Instruction Set Computing

In electronics and computer science, a reduced instruction set computer (RISC) is a computer architecture designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set computer (CISC), a RISC computer might require more instructions (more code) in order to accomplish a task because the individual instructions perform simpler operations. The goal is to offset the need to process more instructions by increasing the speed of each instruction, in particular by implementing an instruction pipeline, which may be simpler to achieve given simpler instructions. The key operational concept of the RISC computer is that each instruction performs only one function (e.g. copy a value from memory to a register). The RISC computer usually has many (16 or 32) high-speed, general-purpose registers with a load–store architecture in which the code for the register-register instructions (for performin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Linux Kernel

The Linux kernel is a Free and open-source software, free and open source Unix-like kernel (operating system), kernel that is used in many computer systems worldwide. The kernel was created by Linus Torvalds in 1991 and was soon adopted as the kernel for the GNU operating system (OS) which was created to be a free software, free replacement for Unix. Since the late 1990s, it has been included in many Linux distributions, operating system distributions, many of which are called Linux. One such Linux kernel operating system is Android (operating system), Android which is used in many mobile and embedded devices. Most of the kernel code is written in C (programming language), C as supported by the GNU compiler collection (GCC) which has extensions beyond standard C. The code also contains assembly language, assembly code for architecture-specific logic such as optimizing memory use and task execution. The kernel has a Modular programming, modular design such that modules can be inte ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Million Instructions Per Second

Instructions per second (IPS) is a measure of a computer's processor speed. For complex instruction set computers (CISCs), different instructions take different amounts of time, so the value measured depends on the instruction mix; even for comparing processors in the same family the IPS measurement can be problematic. Many reported IPS values have represented "peak" execution rates on artificial instruction sequences with few branches and no cache contention, whereas realistic workloads typically lead to significantly lower IPS values. Memory hierarchy also greatly affects processor performance, an issue barely considered in IPS calculations. Because of these problems, synthetic benchmarks such as Dhrystone are now generally used to estimate computer performance in commonly used applications, and raw IPS has fallen into disuse. The term is commonly used in association with a metric prefix (k, M, G, T, P, or E) to form kilo instructions per second (kIPS), mega instructio ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Synchronous Dynamic Random-access Memory

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to the early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions delayed only by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''banks'', allowing the device to operate on a memor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Universal Serial Bus

Universal Serial Bus (USB) is an industry standard, developed by USB Implementers Forum (USB-IF), for digital data transmission and power delivery between many types of electronics. It specifies the architecture, in particular the physical interfaces, and communication protocols to and from ''hosts'', such as personal computers, to and from peripheral ''devices'', e.g. displays, keyboards, and mass storage devices, and to and from intermediate ''hubs'', which multiply the number of a host's ports. Introduced in 1996, USB was originally designed to standardize the connection of peripherals to computers, replacing various interfaces such as serial ports, parallel ports, game ports, and Apple Desktop Bus (ADB) ports. Early versions of USB became commonplace on a wide range of devices, such as keyboards, mice, cameras, printers, scanners, flash drives, smartphones, game consoles, and power banks. USB has since evolved into a standard to replace virtually all common ports on ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |