|

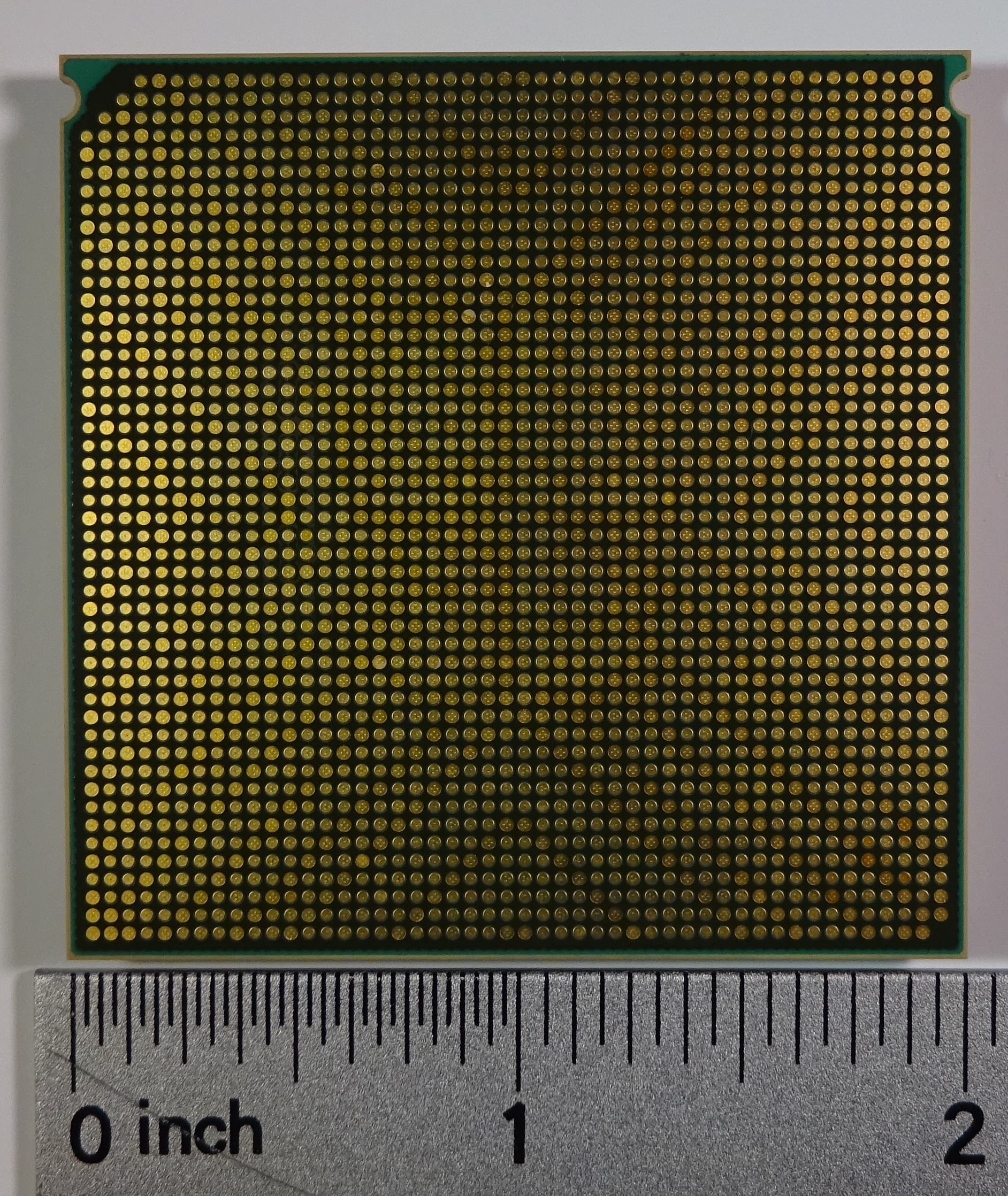

Power6 Ceramic Base

The POWER6 is a microprocessor developed by IBM that implemented the Power ISA v.2.05. When it became available in systems in 2007, it succeeded the POWER5+ as IBM's flagship Power microprocessor. It is claimed to be part of the eCLipz project, said to have a goal of converging IBM's server hardware where practical (hence "ipz" in the acronym: iSeries, pSeries, and zSeries). History POWER6 was described at the International Solid-State Circuits Conference (ISSCC) in February 2006, and additional details were added at the Microprocessor Forum in October 2006 and at the next ISSCC in February 2007. It was formally announced on May 21, 2007. It was released on June 8, 2007 at speeds of 3.5, 4.2 and 4.7 GHz, but the company has noted prototypes have reached 6 GHz. POWER6 reached first silicon in the middle of 2005, and was bumped to 5.0 GHz in May 2008 with the introduction of the P595. Description The POWER6 is a dual-core processor. Each core is capable of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Power ISA

Power ISA is a reduced instruction set computer (RISC) instruction set architecture (ISA) currently developed by the OpenPOWER Foundation, led by IBM. It was originally developed by IBM and the now-defunct Power.org industry group. Power ISA is an evolution of the PowerPC ISA, created by the mergers of the core PowerPC ISA and the optional Book E for embedded applications. The merger of these two components in 2006 was led by Power.org founders IBM and Freescale Semiconductor. Prior to version 3.0, the ISA is divided into several categories. Processors implement a set of these categories as required for their task. Different classes of processors are required to implement certain categories, for example a server-class processor includes the categories: ''Base'', ''Server'', ''Floating-Point'', ''64-Bit'', etc. All processors implement the Base category. Power ISA is a RISC load/store architecture. It has multiple sets of registers: * ''32'' × 32-bit or 64-bit general- ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM ViVA

ViVA (Virtual Vector Architecture) is a technology from IBM for coupling together multiple scalar floating point units to act as a single vector processor. Certain computing tasks are more efficiently handled through vector computations where an instruction can be applied to multiple elements simultaneously, rather than the scalar approach where one instruction is applied to one piece of data at a time. This kind of technology is highly sought after for scientific computing and is IBM's answer to the vector-based supercomputers pioneered by Cray and that was the basis for NEC's Earth Simulator which was the fastest supercomputer in the world 2002-2004. ViVA was developed and implemented by IBM together with National Energy Research Scientific Computing Center inside the Blue Planet project where they had 8 dual core POWER5 processors made into one vector processor capable of approximately 60-80 GFLOPS of computing power. ViVA technology is in use in the ASC Purple ASC Purple wa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

InformationWeek

''InformationWeek'' is a digital magazine which conducts corresponding face-to-face events, virtual events, and research. It is headquartered in San Francisco, California California () is a U.S. state, state in the Western United States that lies on the West Coast of the United States, Pacific Coast. It borders Oregon to the north, Nevada and Arizona to the east, and shares Mexico–United States border, an ... and was first published in 1985 by CMP Media, later became part of Informa TechTarget. The print edition of the magazine has ceased, with the last issue published on June 24, 2013. History The print edition began in 1985 using the name ''Information Week''. * April 1999 - Information Week began its 14th international edition: Brazil. * May 1997 through 2000 – The worldwide regional publications of '' LAN Magazine'' were renamed to the already existing ''Network Magazine''. Networkmagazine.com and lanmag.com now redirect to informationweek.com * September 200 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM System Z10

IBM System z10 is a line of IBM Mainframe computer, mainframes. The z10 Enterprise Class (EC) was announced on February 26, 2008. On October 21, 2008, IBM announced the z10 Business Class (BC), a scaled-down version of the z10 EC. The System z10 represents the first model family powered by the IBM z10 (microprocessor), z10 quad core processing engine. Its successors are the zEnterprise System models introduced in 2010 and 2012. Features Processors The number of "characterizable" (or configurable) processing units (PUs) is indicated in the ''hardware'' model designation (e.g., the E26 has 26 characterizable PUs). Depending on the ''capacity'' model, a PU can be characterized as a IBM z10 (microprocessor), Central Processor (CP), Integrated Facility for Linux (IFL) processor, z Application Assist Processor (zAAP), zIIP, z10 Integrated Information Processor (zIIP), or Internal Coupling Facility (ICF) processor. (The specialty processors are all identical and IBM locks out certai ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM Z10

The z10 is a microprocessor chip made by IBM for their System z10 mainframe computers, released February 26, 2008. It was called "z6" during development. Description The processor implements the CISC z/Architecture and has four cores. Each core has a 64 KB L1 instruction cache, a 128 KB L1 data cache and a 3 MB L2 cache (called the L1.5 cache by IBM). Finally, there is a 24 MB shared L3 cache (referred to as the L2 cache by IBM). The chip measures 21.7×20.0 mm and consists of 993 million transistors fabricated in IBM's 65 nm SOI fabrication process (CMOS 11S), supporting speeds of 4.4 GHz and above – more than twice the clock speed as former mainframes – with a 15 FO4 cycle. Each z10 chip has two 48 GB/s (48 billion bytes per second) SMP hub ports, four 13 GB/s memory ports, two 17 GB/s I/O ports, and 8765 contacts. The z10 processor was co-developed with and shares many design traits with the POWER6 processor, such as fabrication technology, logi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Decimal128

In computing, decimal128 is a decimal floating-point computer number format, number format that occupies 128 bits in computer memory, memory. Formally introduced in IEEE 754-2008, it is intended for applications where it is necessary to emulate decimal rounding exactly, such as financial and tax computations. Format The decimal128 format supports 34 decimal digits of significand and an exponent range of −6143 to +6144, i.e. to . Because the significand is not normalized, most values with less than 34 significant digits have multiple possible representations; , etc. This set of representations for a same value is called a ''Cohort (floating point), cohort''. Zero has 12288 possible representations (24576 if both signed zeros are included, in two different cohorts). Encoding of decimal128 values The IEEE 754 standard allows two alternative encodings for decimal128 values: * The binary encoding, based on binary integer decimal (BID): The significand is encoded as a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Binary128

In computing, quadruple precision (or quad precision) is a binary Floating-point arithmetic, floating-point–based computer number format that occupies 16 bytes (128 bits) with precision at least twice the 53-bit Double-precision floating-point format, double precision. This 128-bit quadruple precision is designed not only for applications requiring results in higher than double precision, but also, as a primary function, to allow the computation of double precision results more reliably and accurately by minimising overflow and round-off errors in intermediate calculations and scratch variables. William Kahan, primary architect of the original IEEE 754 floating-point standard noted, "For now the extended precision#x86 Architecture Extended Precision Format, 10-byte Extended format is a tolerable compromise between the value of extra-precise arithmetic and the price of implementing it to run fast; very soon two more bytes of precision will become tolerable, and ultimately a 16-by ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Floating-point

In computing, floating-point arithmetic (FP) is arithmetic on subsets of real numbers formed by a ''significand'' (a Sign (mathematics), signed sequence of a fixed number of digits in some Radix, base) multiplied by an integer power of that base. Numbers of this form are called floating-point numbers. For example, the number 2469/200 is a floating-point number in base ten with five digits: 2469/200 = 12.345 = \! \underbrace_\text \! \times \! \underbrace_\text\!\!\!\!\!\!\!\overbrace^ However, 7716/625 = 12.3456 is not a floating-point number in base ten with five digits—it needs six digits. The nearest floating-point number with only five digits is 12.346. And 1/3 = 0.3333… is not a floating-point number in base ten with any finite number of digits. In practice, most floating-point systems use Binary number, base two, though base ten (decimal floating point) is also common. Floating-point arithmetic operations, such as addition and division, approximate the correspond ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IEEE 754

The IEEE Standard for Floating-Point Arithmetic (IEEE 754) is a technical standard for floating-point arithmetic originally established in 1985 by the Institute of Electrical and Electronics Engineers (IEEE). The standard #Design rationale, addressed many problems found in the diverse floating-point implementations that made them difficult to use reliably and Software portability, portably. Many hardware floating-point units use the IEEE 754 standard. The standard defines: * ''arithmetic formats:'' sets of Binary code, binary and decimal floating-point data, which consist of finite numbers (including signed zeros and subnormal numbers), infinity, infinities, and special "not a number" values (NaNs) * ''interchange formats:'' encodings (bit strings) that may be used to exchange floating-point data in an efficient and compact form * ''rounding rules:'' properties to be satisfied when rounding numbers during arithmetic and conversions * ''operations:'' arithmetic and other operatio ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Decimal Floating Point

Decimal floating-point (DFP) arithmetic refers to both a representation and operations on Decimal data type, decimal floating-point numbers. Working directly with decimal (base-10) fractions can avoid the rounding errors that otherwise typically occur when converting between decimal fractions (common in human-entered data, such as measurements or financial information) and binary (base-2) fractions. The advantage of decimal floating-point representation over decimal Fixed-point arithmetic, fixed-point and Integer (computer science), integer representation is that it supports a much wider range of values. For example, while a fixed-point representation that allocates 8 decimal digits and 2 decimal places can represent the numbers 123456.78, 8765.43, 123.00, and so on, a floating-point representation with 8 decimal digits could also represent 1.2345678, 1234567.8, 0.000012345678, 12345678000000000, and so on. This wider range can dramatically slow the accumulation of rounding error ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Floating Point Unit

A floating-point unit (FPU), numeric processing unit (NPU), colloquially math coprocessor, is a part of a computer system specially designed to carry out operations on floating-point numbers. Typical operations are addition, subtraction, multiplication, division, and square root. Modern designs generally include a fused multiply-add instruction, which was found to be very common in real-world code. Some FPUs can also perform various transcendental functions such as exponential or trigonometric calculations, but the accuracy can be low, so some systems prefer to compute these functions in software. Floating-point operations were originally handled in software in early computers. Over time, manufacturers began to provide standardized floating-point libraries as part of their software collections. Some machines, those dedicated to scientific processing, would include specialized hardware to perform some of these tasks with much greater speed. The introduction of microcode in the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |