|

QorIQ

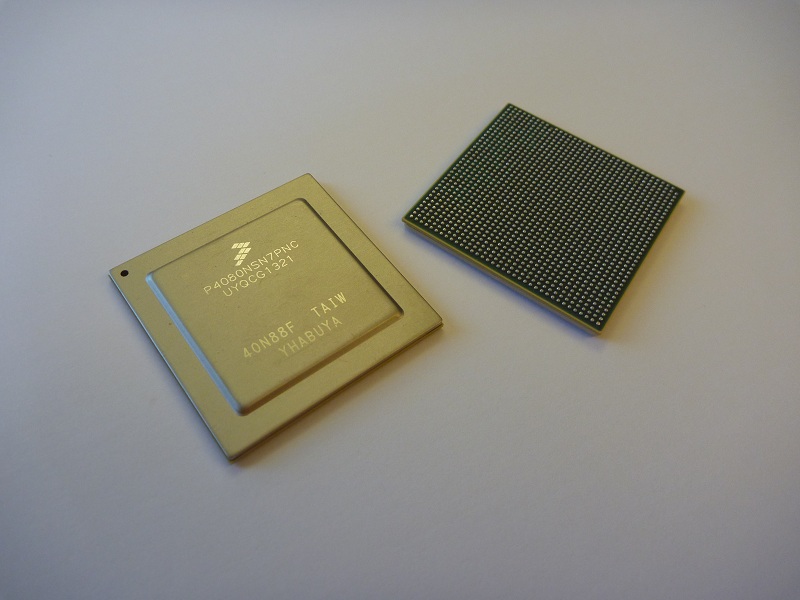

QorIQ is a brand of ARM-based and Power ISA-based communications microprocessors from NXP Semiconductors (formerly Freescale). It is the evolutionary step from the PowerQUICC platform, and initial products were built around one or more e500mc cores and came in five different product platforms, P1, P2, P3, P4, and P5, segmented by performance and functionality. The platform keeps software compatibility with older PowerPC products such as the PowerQUICC platform. In 2012 Freescale announced ARM-based QorIQ offerings beginning in 2013. The QorIQ brand and the P1, P2 and P4 product families were announced in June 2008. Details of P3 and P5 products were announced in 2010. QorIQ P Series processors were manufactured on a 45 nm fabrication process and was available in the end of 2008 (P1 and P2), mid-2009 (P4) and 2010 (P5). QorIQ T Series is based on a 28 nm process and is pushing a very aggressive power envelope target, capping at 30 W. These are using the e6500 core with ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerPC E500

The PowerPC e500 is a 32-bit microprocessor core from Freescale Semiconductor. The core is compatible with the older PowerPC Book E specification as well as the Power ISA v.2.03. It has a dual issue, seven-stage pipeline with FPUs (from version 2 onwards), 32/32 KiB data and instruction L1 caches and 256, 512 or 1024 KiB L2 frontside cache. Speeds range from 533 MHz up to 1.5 GHz, and the core is designed to be highly configurable and meet the specific needs of embedded applications with features like multi-core operation interface for auxiliary application processing units (APU). e500 powers the high-performance PowerQUICC III system on a chip (SoC) network processors and they all share a common naming scheme, ''MPC85xx''. Freescale's new QorIQ is the evolutionary step from PowerQUICC III and will also be based on e500 cores. Versions There are three versions of the e500 core, namely the original ''e500v1'', the ''e500v2'' and the ''e500mc''. A 6 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerQUICC

PowerQUICC is the name for several PowerPC- and Power ISA-based microcontrollers from Freescale Semiconductor. They are built around one or more PowerPC cores and the Communications Processor Module ( QUICC Engine) which is a separate RISC core specialized in such tasks such as I/O, communications, ATM, security acceleration, networking and USB. Many components are System-on-a-chip designs tailor-made for embedded applications. PowerQUICC processors are used in networking, automotive, industrial, storage, printing and consumer applications. Freescale are using PowerQUICC processors as a part of their mobileGT platform. Freescale also manufactures QUICC microcontrollers based on the older 68k technology. There are four distinct lines of processors, mainly based on processing power. PowerQUICC I The MPC8xx family was Motorola's first PowerPC based embedded processors, suited for network processors and system-on-a-chip devices. The core is an original implementation of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Data Path Acceleration Architecture

The QorIQ Data Path Acceleration Architecture or QorIQ DPAA is a architecture which integrates aspects of packet Packet may refer to: * A small container or pouch ** Packet (container), a small single use container ** Cigarette packet ** Sugar packet * Network packet, a formatted unit of data carried by a packet-mode computer network * Packet radio, a form ... processing in the SoC, thereby addressing issues and requirements resulting from the multicore nature of QorIQ SoCs. The DPAA includes Cores, Network and packet I/O as well as hardware offload accelerators. The DPAA can be used to address various performance related requirements, especially those created by the high speed network I/O found on multicore SoCs such as the P4080. References External links * http://freescalesemi.com.cn/cstory/ftf/2009/download/net_f0279.pdf * http://www.electropages.com/2010/08/freescale-three-new-qoriq-processors-incorporate-data-path-acceleration/ * http://cache.freescale.com/fil ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

NXP Semiconductors

NXP Semiconductors N.V. (NXP) is a Dutch semiconductor designer and manufacturer with headquarters in Eindhoven, Netherlands. The company employs approximately 31,000 people in more than 30 countries. NXP reported revenue of $11.06 billion in 2021. Originally spun off from Philips in 2006, NXP completed its initial public offering, on August 6, 2010, with shares trading on NASDAQ under the ticker symbol ''NXPI''. On December 23, 2013, NXP Semiconductors was added to the NASDAQ 100. On March 2, 2015, it was announced that NXP would merge with Freescale Semiconductor. The merger was closed on December 7, 2015. On October 27, 2016, it was announced that Qualcomm would try to buy NXP. Because the Chinese merger authority did not approve the acquisition before the deadline set by Qualcomm, the attempt was effectively cancelled on July 26, 2018. Description NXP provides technology solutions targeting the automotive, industrial & IoT, mobile, and communication infrastructure market ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A9

The ARM Cortex-A9 MPCore is a 32-bit multi-core processor that provides up to 4 cache-coherent cores, each implementing the ARM v7 architecture instruction set. It was introduced in 2007. Features Key features of the Cortex-A9 core are: * Out-of-order speculative issue superscalar execution 8-stage pipeline giving 2.50 DMIPS/MHz/core. * NEON SIMD instruction set extension performing up to 16 operations per instruction (optional). * High performance VFPv3 floating point unit doubling the performance of previous ARM FPUs (optional). * Thumb-2 instruction set encoding reduces the size of programs with little impact on performance. * TrustZone security extensions. * Jazelle DBX support for Java execution. * Jazelle RCT for JIT compilation. * Program Trace Macrocell and CoreSight Design Kit for non-intrusive tracing of instruction execution. * L2 cache controller (0–4 MB). * Multi-core processing. ARM states that the TSMC 40G hard macro implementation typically ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A7 The ARM Cortex-A7 MPCore is a 32-bit microprocessor core licensed by ARM Holdings implementing the ARM architecture#AArch32, ARMv7-A architecture announced in 2011. Overview It has two target applications; firstly as a smaller, simpler, and more power-efficient successor to the ARM Cortex-A8, Cortex-A8. The other use is in the big.LITTLE architecture, combining one or more A7 cores with one or more ARM Cortex-A15 MPCore, Cortex-A15 cores into a heterogeneous computing, heterogeneous system. To do this it is fully feature-compatible with the A15. Key features of the Cortex-A7 core are: * Superscalar, Partial dual-issue, out-of-order execution, in-order microarchitecture with an 8-stage instruction pipeline, pipeline * ARM architecture#Advanced SIMD (NEON), NEON SIMD instruction set extension * VFPv4 Floating Point Unit * Thumb-2 instruction set encoding * Jazelle RCT * Hardware virtualization * Large Page Address Extensio |