|

POWER5

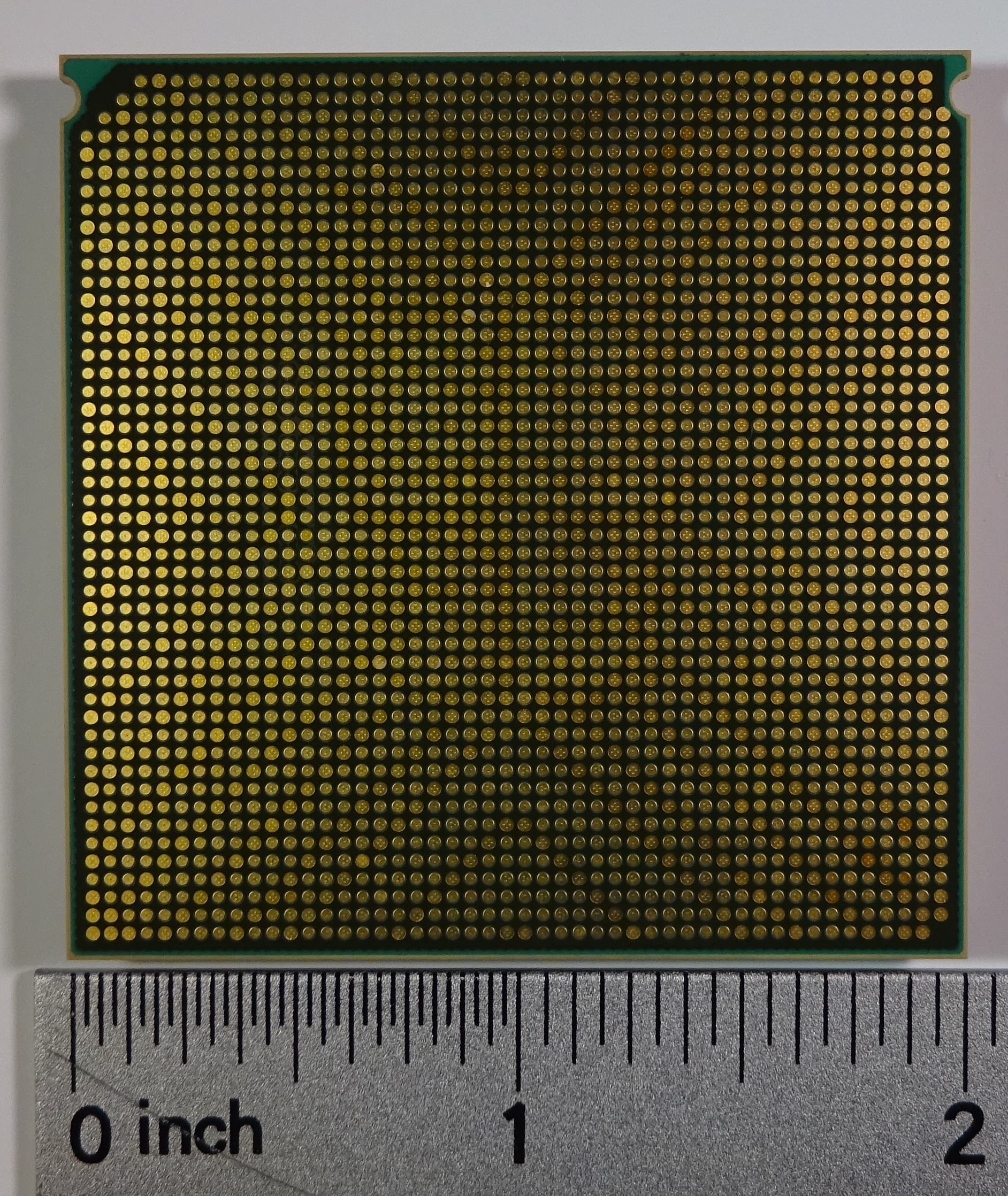

The POWER5 is a microprocessor developed and fabricated by IBM. It is an improved version of the POWER4. The principal improvements are support for simultaneous multithreading (SMT) and an on-die memory controller. The POWER5 is a dual-core microprocessor, with each core supporting one physical Thread (computing), thread and two logical threads, for a total of two physical threads and four logical threads. History Technical details of the microprocessor were first presented at the 2003 Hot Chips (symposium), Hot Chips conference. A more complete description was given at Microprocessor Forum 2003 on 14 October 2003. The POWER5 was not sold openly and was used exclusively by IBM and their partners. Systems using the microprocessor were introduced in 2004. The POWER5 competed in the high-end enterprise server market, mostly against the Intel Itanium 2 and to a lesser extent, the Sun Microsystems UltraSPARC IV and the Fujitsu SPARC64 V. It was superseded in 2005 by an improve ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

System p

The IBM System p is a high-end line of RISC ( Power)/UNIX-based servers. It was the successor of the RS/6000 line, and predecessor of the IBM Power Systems server series. History The previous RS/6000 line was originally a line of workstations and servers. The first System p server line was named the ''e''Server pSeries in 2000 as part of the e-Server branding initiative. In 2004, with the advent of the POWER5 processor, the server family was rebranded the ''e''Server p5. In 2005, following IBM's move to streamline its server and storage brands worldwide, and incorporating the "System" brand with the Systems Agenda, the family was again renamed to System p5. The System p5 now encompassed the IBM OpenPower product line. In 2007, after the introduction of the POWER6 processor models, the last rename under the System p brand dropped the p (numbered) designation. In April 2008, IBM announced a rebranding of the System p and its unification with the mid-range System i platform. T ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

POWER6

The POWER6 is a microprocessor developed by IBM that implemented the Power ISA#Power ISA v.2.05, Power ISA v.2.05. When it became available in systems in 2007, it succeeded the POWER5#POWER5+, POWER5+ as IBM's flagship Power microprocessor. It is claimed to be part of the eCLipz project, said to have a goal of converging IBM's server hardware where practical (hence "ipz" in the acronym: IBM AS/400, iSeries, pSeries, and zSeries). History POWER6 was described at the International Solid-State Circuits Conference (ISSCC) in February 2006, and additional details were added at the Microprocessor Forum in October 2006 and at the next ISSCC in February 2007. It was formally announced on May 21, 2007. It was released on June 8, 2007 at speeds of 3.5, 4.2 and 4.7 GHz, but the company has noted prototypes have reached 6 GHz. POWER6 reached first silicon in the middle of 2005, and was bumped to 5.0 GHz in May 2008 with the introduction of the P595. Description The POWE ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM AS/400

The IBM AS/400 (Application System/400) is a family of midrange computers from IBM announced in June 1988 and released in August 1988. It was the successor to the System/36 and System/38 platforms, and ran the OS/400 operating system. Lower-cost but more powerful than its predecessors, an estimated 111,000 installations existed by the end of 1990 and annual revenue reaching $14 billion that year, increasing to 250,000 systems by 1994, and about 500,000 shipped by 1997. A key concept in the AS/400 platform is IBM i#TIMI, Technology Independent Machine Interface (TIMI), a platform-independent instruction set architecture (ISA) that is translated to native machine language instructions. The platform has used this capability to change the underlying processor architecture without breaking application compatibility. Early systems were based on a 48-bit Complex instruction set computer, CISC instruction set architecture known as the ''Internal Microprogrammed Interface'' (IMPI), original ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multi-Chip Module

A multi-chip module (MCM) is generically an electronic assembly (such as a package with a number of conductor terminals or Lead (electronics), "pins") where multiple integrated circuits (ICs or "chips"), semiconductor Die (integrated circuit), dies and/or other discrete components are integrated, usually onto a unifying substrate, so that in use it can be treated as if it were a larger IC. Other terms for MCM packaging include "heterogeneous integration" or "hybrid integrated circuit". The advantage of using MCM packaging is it allows a manufacturer to use multiple components for modularity and/or to improve yields over a conventional monolithic IC approach. A Flip Chip Multi-Chip Module (FCMCM) is a multi-chip module that uses flip chip technology. A FCMCM may have one large die and several smaller dies all on the same module. Overview Multi-chip modules come in a variety of forms depending on the complexity and development philosophies of their designers. These can range from ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM ViVA

ViVA (Virtual Vector Architecture) is a technology from IBM for coupling together multiple scalar floating point units to act as a single vector processor. Certain computing tasks are more efficiently handled through vector computations where an instruction can be applied to multiple elements simultaneously, rather than the scalar approach where one instruction is applied to one piece of data at a time. This kind of technology is highly sought after for scientific computing and is IBM's answer to the vector-based supercomputers pioneered by Cray and that was the basis for NEC's Earth Simulator which was the fastest supercomputer in the world 2002-2004. ViVA was developed and implemented by IBM together with National Energy Research Scientific Computing Center inside the Blue Planet project where they had 8 dual core POWER5 processors made into one vector processor capable of approximately 60-80 GFLOPS of computing power. ViVA technology is in use in the ASC Purple ASC Purple wa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multithreading (computer Architecture)

In computer architecture, multithreading is the ability of a central processing unit (CPU) (or a single core in a multi-core processor) to provide multiple threads of execution. Overview The multithreading paradigm has become more popular as efforts to further exploit instruction-level parallelism have stalled since the late 1990s. This allowed the concept of throughput computing to re-emerge from the more specialized field of transaction processing. Even though it is very difficult to further speed up a single thread or single program, most computer systems are actually multitasking among multiple threads or programs. Thus, techniques that improve the throughput of all tasks result in overall performance gains. Two major techniques for throughput computing are ''multithreading'' and ''multiprocessing''. Advantages If a thread gets a lot of cache misses, the other threads can continue taking advantage of the unused computing resources, which may lead to faster overall exe ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |