|

Intel Xeon Chipsets

Around the time that the Pentium 4 processor was introduced, Intel's Xeon line diverged from its line of desktop processors, which at the time was using the Pentium branding. The divergence was implemented by using different sockets; since then, the sockets for Xeon chips have tended to remain constant across several generations of implementation. The chipsets contain a 'memory controller hub' and an 'I/O controller hub', which tend to be called 'north bridge' and 'south bridge' respectively. The memory controller hub connects to the processors, memory, high-speed I/O such as PCI Express, and to the I/O controller hub by a proprietary link. The I/O controller hub, on the other hand, connects to lower-speed I/O, such as SATA, PCI, USB, and Ethernet. P6 (microarchitecture), P6-based Xeon chipsets Dual processor P6 (microarchitecture), P6-based Xeon chipsets Intel's initial preferred chipset for Pentium III Xeon was the 840. Four processor P6 (microarchitecture), P6-based ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Pentium 4

Pentium 4 is a series of single-core central processing unit, CPUs for Desktop computer, desktops, laptops and entry-level Server (computing), servers manufactured by Intel. The processors were shipped from November 20, 2000 until August 8, 2008. All Pentium 4 CPUs are based on the NetBurst microarchitecture, the successor to the P6 (microarchitecture), P6. The Pentium 4 #Willamette, Willamette (180 nm) introduced SSE2, while the #Prescott, Prescott (90 nm) introduced SSE3 and later 64-bit technology. Later versions introduced Hyper-threading, Hyper-Threading Technology (HTT). The first Pentium 4-branded processor to implement x86-64, 64-bit was the Prescott (90 nm) (February 2004), but this feature was not enabled. Intel subsequently began selling 64-bit Pentium 4s using the ''"E0" revision'' of the Prescotts, being sold on the OEM market as the Pentium 4, model F. The E0 revision also adds eXecute Disable (XD) (Intel's name for the NX bit) to Intel 64. Int ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Snoop Filter

Bus snooping or bus sniffing is a scheme by which a coherency controller (snooper) in a cache (a snoopy cache) monitors or snoops the bus transactions, and its goal is to maintain a cache coherency in distributed shared memory systems. This scheme was introduced by Ravishankar and Goodman in 1983, under the name "write-once" cache coherency. A cache containing a coherency controller (snooper) is called a snoopy cache. How it works When specific data are shared by several caches and a processor modifies the value of the shared data, the change must be propagated to all the other caches which have a copy of the data. This change propagation prevents the system from violating cache coherency. The notification of data change can be done by bus snooping. All the snoopers monitor every transaction on a bus. If a transaction modifying a shared cache block appears on a bus, all the snoopers check whether their caches have the same copy of the shared block. If a cache has a copy of the s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Panther Point

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chipsa northbridge and southbridge, and first appeared in the Intel 5 Series. The PCH controls certain data paths and support functions used in conjunction with Intel CPUs. These include clocking (the system clock), Flexible Display Interface (FDI) and Direct Media Interface (DMI), although FDI is used only when the chipset is required to support a processor with integrated graphics. As such, I/O functions are reassigned between this new central hub and the CPU compared to the previous architecture: some northbridge functions, the memory controller and PCIe lanes, were integrated into the CPU while the PCH took over the remaining functions in addition to the traditional roles of the southbridge. AMD has its equivalent for the PCH, known simply as a chipset since the release of the Zen architecture in 2017. A ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ivy Bridge (microarchitecture)

Ivy Bridge is the codename for Intel's 22 nm microarchitecture used in the third generation of the Intel Core processors ( Core i7, i5, i3). Ivy Bridge is a die shrink to 22 nm process based on FinFET ("3D") Tri-Gate transistors, from the former generation's 32 nm Sandy Bridge microarchitecture—also known as tick–tock model. The name is also applied more broadly to the Xeon and Core i7 Extreme Ivy Bridge-E series of processors released in 2013. Ivy Bridge processors are backward compatible with the Sandy Bridge platform, but such systems might require a firmware update (vendor specific). In 2011, Intel released the 7-series Panther Point chipsets with integrated USB 3.0 and SATA 3.0 to complement Ivy Bridge. Volume production of Ivy Bridge chips began in the third quarter of 2011. Quad-core and dual-core-mobile models launched on April 29, 2012 and May 31, 2012 respectively. Core i3 desktop processors, as well as the first 22 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cave Creek (PCH)

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chipsa northbridge and southbridge, and first appeared in the Intel 5 Series. The PCH controls certain data paths and support functions used in conjunction with Intel CPUs. These include clocking (the system clock), Flexible Display Interface (FDI) and Direct Media Interface (DMI), although FDI is used only when the chipset is required to support a processor with integrated graphics. As such, I/O functions are reassigned between this new central hub and the CPU compared to the previous architecture: some northbridge functions, the memory controller and PCIe lanes, were integrated into the CPU while the PCH took over the remaining functions in addition to the traditional roles of the southbridge. AMD has its equivalent for the PCH, known simply as a chipset since the release of the Zen architecture in 2017. AM ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Gigabaud

In telecommunications and electronics, baud (; symbol: Bd) is a common unit of measurement of symbol rate, which is one of the components that determine the speed of communication over a data channel. It is the unit for symbol rate or modulation rate in symbols per second or pulses per second. It is the number of distinct symbol changes (signalling events) made to the transmission medium per second in a digitally modulated signal or a bd rate line code. Baud is related to ''gross bit rate'', which can be expressed in bits per second (bit/s). If there are precisely two symbols in the system (typically 0 and 1), then baud and bits per second are equivalent. Naming The baud unit is named after Émile Baudot, the inventor of the Baudot code for telegraphy, and is represented according to the rules for SI units. That is, the first letter of its symbol is uppercase (Bd), but when the unit is spelled out, it should be written in lowercase (baud) except when it begins a sentence or ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Active Management Technology

Intel Active Management Technology (AMT) is hardware and firmware for remote out-of-band management of select business computers, running on the Intel Management Engine, a microprocessor subsystem not exposed to the user, intended for monitoring, maintenance, updating, and repairing systems. Out-of-band (OOB) or hardware-based management is different from software-based (or in-band) management and software management agents. Hardware-based management works at a different level from software applications and uses a communication channel (through the TCP/IP stack) that is different from software-based communication (which is through the software stack in the operating system). Hardware-based management does not depend on the presence of an OS or a locally installed management agent. Hardware-based management has been available on Intel/AMD-based computers in the past, but it has largely been limited to auto-configuration using DHCP or BOOTP for dynamic IP address allocation and di ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cougar Point

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chipsa northbridge and southbridge, and first appeared in the Intel 5 Series. The PCH controls certain data paths and support functions used in conjunction with Intel CPUs. These include clocking (the system clock), Flexible Display Interface (FDI) and Direct Media Interface (DMI), although FDI is used only when the chipset is required to support a processor with integrated graphics. As such, I/O functions are reassigned between this new central hub and the CPU compared to the previous architecture: some northbridge functions, the memory controller and PCIe lanes, were integrated into the CPU while the PCH took over the remaining functions in addition to the traditional roles of the southbridge. AMD has its equivalent for the PCH, known simply as a chipset since the release of the Zen architecture in 2017. AM ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of Intel Xeon Microprocessors

The following is a list of Intel Xeon Xeon (; ) is a brand of x86 microprocessors designed, manufactured, and marketed by Intel, targeted at the non-consumer workstation, server, and embedded markets. It was introduced in June 1998. Xeon processors are based on the same archite ... microprocessors, by generation. P6-based Pentium II Xeon * Pentium II Xeon 400 * Pentium II Xeon 400 * Pentium II Xeon 450 * Pentium II Xeon 450 * Pentium II Xeon 450 Pentium III Xeon NetBurst-based Xeon UP/DP Xeon MP Pentium M (Yonah)-based Xeon DP * Xeon LV 1.66 * Xeon LV 2.0 * Xeon LV 2.16 * Xeon ULV 1.66 Core-based Xeon 3000 series * Xeon 3040 * Xeon 3050 * Xeon 3060 * Xeon 3065 * Xeon 3070 * Xeon 3075 * Xeon 3085 * Xeon L3014 * Xeon E3113 * Xeon E3110 * Xeon E3120 * Xeon L3110 * Xeon X3210 * Xeon X3220 * Xeon X3230 * Xeon X3320 * Xeon X3330 * Xeon X3350 * Xeon X3360 * Xeon X3370 * Xeon X3380 * Xeon L3360 * Xeon X3323 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sandy Bridge (microarchitecture)

Sandy Bridge is the codename for Intel's 32 nm microarchitecture used in the second generation of the Intel Core processors ( Core i7, i5, i3). The Sandy Bridge microarchitecture is the successor to Nehalem and Westmere microarchitecture. Intel demonstrated an A1 stepping Sandy Bridge processor in 2009 during Intel Developer Forum (IDF), and released first products based on the architecture in January 2011 under the Core brand. Sandy Bridge is manufactured in the 32 nm process and has a soldered contact with the die and IHS (Integrated Heat Spreader), while Intel's subsequent generation Ivy Bridge uses a 22 nm die shrink and a TIM (Thermal Interface Material) between the die and the IHS. Technology Intel demonstrated a Sandy Bridge processor with A1 stepping at 2 GHz during the Intel Developer Forum in September 2009. Upgraded features from Nehalem include: CPU * Intel Turbo Boost 2.0 * 32 KB data + 32 KB instruction L1 cache and 256 KB L2 c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

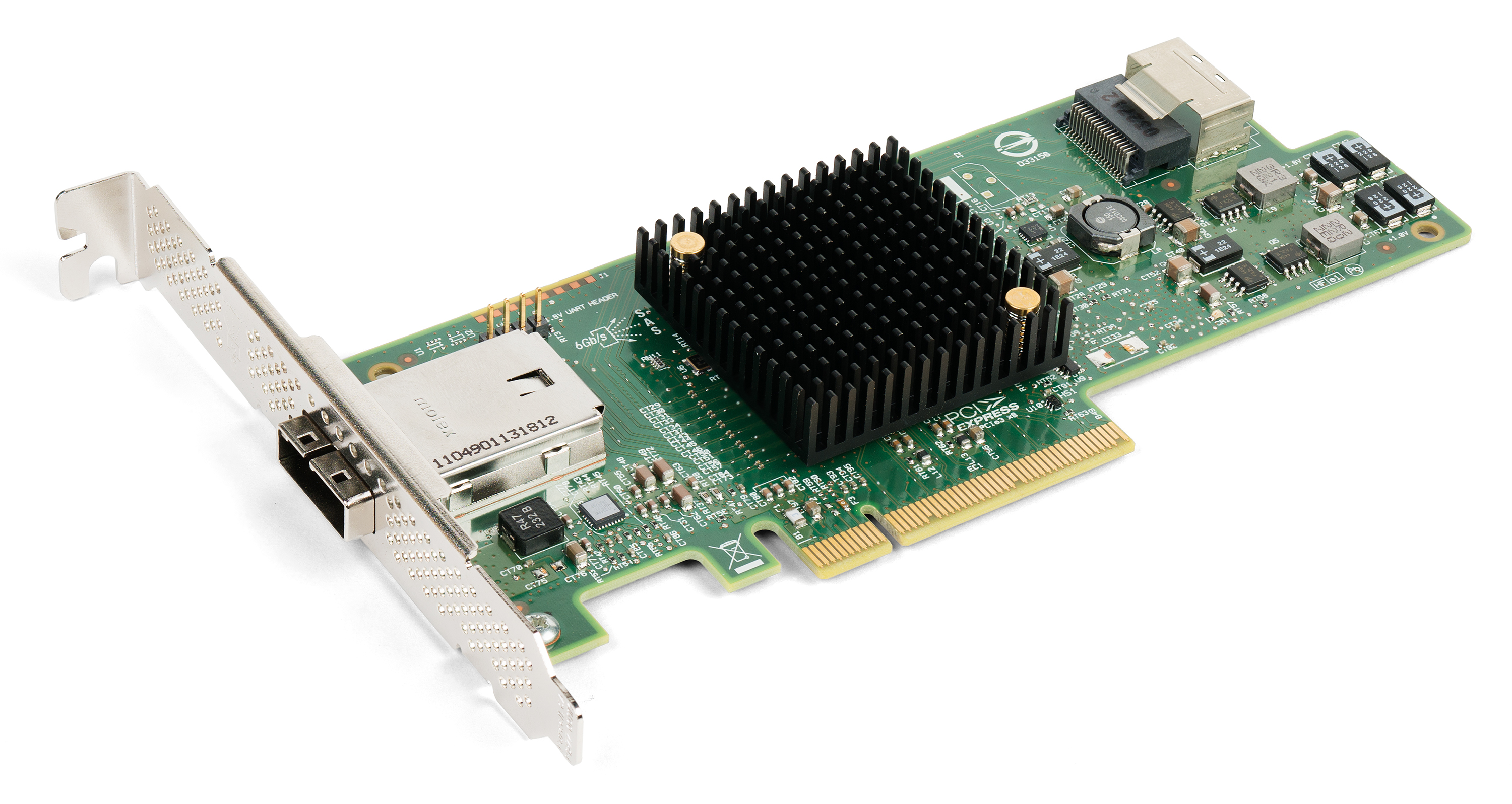

PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe, is a high-speed standard used to connect hardware components inside computers. It is designed to replace older expansion bus standards such as Peripheral Component Interconnect, PCI, PCI-X and Accelerated Graphics Port, AGP. Developed and maintained by the PCI-SIG (PCI Special Interest Group), PCIe is commonly used to connect graphics cards, sound cards, Wi-Fi and Ethernet adapters, and storage devices such as solid-state drives and hard disk drives. Compared to earlier standards, PCIe supports faster data transfer, uses fewer pins, takes up less space, and allows devices to be added or removed while the computer is running (hot swapping). It also includes better error detection and supports newer features like I/O virtualization for advanced computing needs. PCIe connections are made through "lanes," which are pairs of wires that send and receive data. Devices can use one or more lanes ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |