|

Application-specific Integrated Circuits

An application-specific integrated circuit (ASIC ) is an integrated circuit (IC) chip customized for a particular use, rather than intended for general-purpose use, such as a chip designed to run in a digital voice recorder or a high-efficiency video codec. Application-specific standard product chips are intermediate between ASICs and industry standard integrated circuits like the 7400 series or the 4000 series. ASIC chips are typically fabricated using metal–oxide–semiconductor (MOS) technology, as MOS integrated circuit chips. As feature sizes have shrunk and chip design tools improved over the years, the maximum complexity (and hence functionality) possible in an ASIC has grown from 5,000 logic gates to over 100 million. Modern ASICs often include entire microprocessors, memory blocks including ROM, RAM, EEPROM, flash memory and other large building blocks. Such an ASIC is often termed a SoC ( system-on-chip). Designers of digital ASICs often use a hardware descr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

EEPROM

EEPROM or E2PROM (electrically erasable programmable read-only memory) is a type of non-volatile memory. It is used in computers, usually integrated in microcontrollers such as smart cards and remote keyless systems, or as a separate chip device, to store relatively small amounts of data by allowing individual bytes to be erased and reprogrammed. EEPROMs are organized as arrays of floating-gate transistors. EEPROMs can be programmed and erased in-circuit, by applying special programming signals. Originally, EEPROMs were limited to single-byte operations, which made them slower, but modern EEPROMs allow multi-byte page operations. An EEPROM has a limited life for erasing and reprogramming, reaching a million operations in modern EEPROMs. In an EEPROM that is frequently reprogrammed, the life of the EEPROM is an important design consideration. Flash memory is a type of EEPROM designed for high speed and high density, at the expense of large erase blocks (typically 512 b ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

EE Times

''EE Times'' (''Electronic Engineering Times'') is an electronics industry magazine published in the United States since 1972. EE Times is currently owned by AspenCore, a division of Arrow Electronics since August 2016. Ownership and status ''EE Times'' was launched in 1972 by Gerard G. Leeds of CMP Publications Inc. In 1999, the Leeds family sold CMP to United Business Media for $900 million. After 2000, ''EE Times'' moved more into web publishing. The shift in advertising from print to online began to accelerate in 2007, and the periodical shed staff to adjust to the downturn in revenue. In July 2013, the digital edition migrated to UBM TechWeb's DeusM community platform. On June 3, 2016, UBM announced that ''EE Times'', along with the rest of its electronics media portfolio ( EDN, Embedded.com, TechOnline, and Datasheets.com), was being sold to AspenCore Media, a company owned by Arrow Electronics, for $23.5 million. The acquisition was completed on August 1, 2016. A ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Amortized Cost

The historical cost of an asset at the time it is acquired or created is the value of the costs incurred in acquiring or creating the asset, comprising the consideration paid to acquire or create the asset plus transaction costs. Historical cost accounting involves reporting assets and liabilities at their historical costs, which are not updated for changes in the items' values. Consequently, the amounts reported for these balance sheet items often differ from their current economic or market values. While use of historical cost measurement is criticised for its lack of timely reporting of value changes, it remains in use in most accounting systems during periods of low and high inflation and deflation. During hyperinflation, International Financial Reporting Standards (IFRS) require financial capital maintenance in units of constant purchasing power in terms of the monthly CPI as set out in IAS 29, Financial Reporting in Hyperinflationary Economies. Various adjustments to hist ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Mass Production

Mass production, also known as mass production, series production, series manufacture, or continuous production, is the production of substantial amounts of standardized products in a constant flow, including and especially on assembly lines. Together with job production and batch production, it is one of the three main production methods. The term ''mass production'' was popularized by a 1926 article in the ''Encyclopædia Britannica'' supplement that was written based on correspondence with Ford Motor Company. ''The New York Times'' used the term in the title of an article that appeared before the publication of the ''Britannica'' article. The idea of mass production is applied to many kinds of products: from fluids and particulates handled in bulk (food, fuel, chemicals and mined minerals), to clothing, textiles, parts and assemblies of parts ( household appliances and automobiles). Some mass production techniques, such as standardized sizes and production lines, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FPGA Prototyping

Field-programmable gate array prototyping (FPGA prototyping), also referred to as FPGA-based prototyping, ASIC prototyping or system-on-chip (SoC) prototyping, is the method to prototype system-on-chip and application-specific integrated circuit designs on FPGAs for hardware verification and early software development. Verification methods for hardware design as well as early software and firmware co-design have become mainstream. Prototyping SoC and ASIC designs with one or more FPGAs and electronic design automation (EDA) software has become a good method to do this. Importance #Running a SoC design on FPGA prototype is a reliable way to ensure that it is functionally correct. This is compared to designers only relying on software simulations to verify that their hardware design is sound. About a third of all current SoC designs are fault-free during first silicon pass, with nearly half of all re-spins caused by functional logic errors. A single prototyping platform can ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Non-recurring Engineering

Non-recurring engineering (NRE) cost refers to the one-time cost to research, design, develop and test a new product or product enhancement. When budgeting for a new product, NRE must be considered to analyze if a new product will be profitable. Even though a company will pay for NRE on a project only once, NRE costs can be prohibitively high and the product will need to sell well enough to produce a return on the initial investment. NRE is unlike production costs, which must be paid constantly to maintain production of a product. It is a form of fixed cost in economics terms. Once a system is designed any number of units can be manufactured without increasing NRE cost. NRE can be also budgeted and paid via another commercial term called Royalty Fee. The Royalty Fee could be a percentage of sales revenue or profit or combination of these two, which have to be incorporated in a mid to long term agreement between technology supplier and the OEM. In a project-type (manufacturing) ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

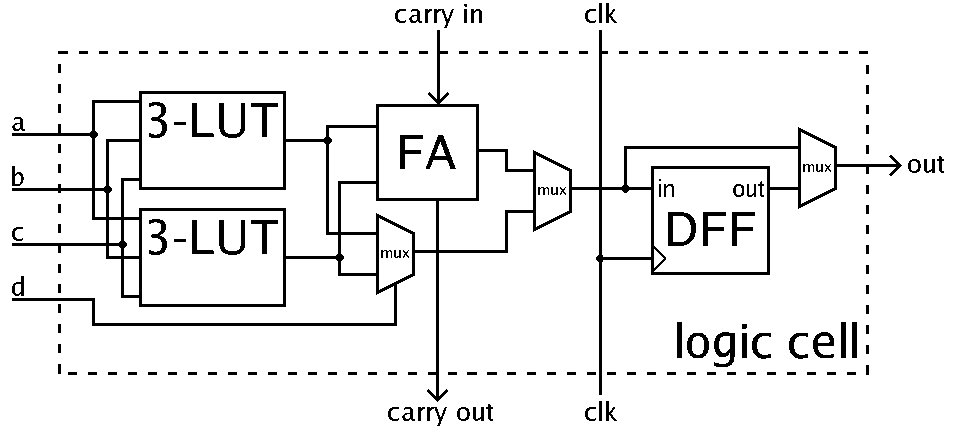

Logic Block

In computing, a logic block or configurable logic block (CLB) is a fundamental building block of field-programmable gate array (FPGA) technology. Logic blocks can be configured by the engineer to provide reconfigurable computing, reconfigurable logic gates. Logic blocks are the most common FPGA architecture, and are usually laid out within a logic block array. Logic blocks require I/O pads (to interface with external signals), and routing channels (to interconnect logic blocks). Programmable logic blocks were invented by David W. Page and LuVerne R. Peterson, and defined within their 1985 patents.Google Patent Search,Re-programmable PLA. Filed January 11, 1983. Granted April 2, 1985. Retrieved February 5, 2009.Google Patent Search,Dynamic data re-programmable PLA. Filed January 11, 1983. Granted June 18, 1985. Retrieved February 5, 2009. Applications An application circuit must be mapped into an FPGA with adequate resources. While the number of logic blocks and I/Os required is e ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |