|

AVX-512

AVX-512 are 512-bit extensions to the 256-bit Advanced Vector Extensions SIMD instructions for x86 instruction set architecture (ISA) proposed by Intel in July 2013, and first implemented in the 2016 Intel Xeon Phi x200 (Knights Landing), and then later in a number of AMD and other Intel CPUs ( see list below). AVX-512 consists of multiple extensions that may be implemented independently. This policy is a departure from the historical requirement of implementing the entire instruction block. Only the core extension AVX-512F (AVX-512 Foundation) is required by all AVX-512 implementations. Besides widening most 256-bit instructions, the extensions introduce various new operations, such as new data conversions, scatter operations, and permutations. The number of AVX registers is increased from 16 to 32, and eight new "mask registers" are added, which allow for variable selection and blending of the results of instructions. In CPUs with the vector length (VL) extension—included in m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Advanced Vector Extensions

Advanced Vector Extensions (AVX, also known as Gesher New Instructions and then Sandy Bridge New Instructions) are SIMD extensions to the x86 instruction set architecture for microprocessors from Intel and Advanced Micro Devices (AMD). They were proposed by Intel in March 2008 and first supported by Intel with the Sandy Bridge microarchitecture shipping in Q1 2011 and later by AMD with the Bulldozer microarchitecture shipping in Q4 2011. AVX provides new features, new instructions, and a new coding scheme. AVX2 (also known as Haswell New Instructions) expands most integer commands to 256 bits and introduces new instructions. They were first supported by Intel with the Haswell microarchitecture, which shipped in 2013. AVX-512 expands AVX to 512-bit support using a new EVEX prefix encoding proposed by Intel in July 2013 and first supported by Intel with the Knights Landing co-processor, which shipped in 2016. In conventional processors, AVX-512 was introduced with Skylak ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Xeon Phi

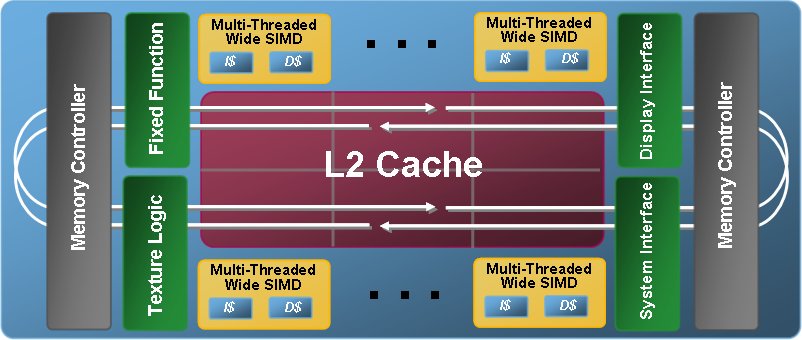

Xeon Phi is a discontinued series of x86 manycore processors designed and made by Intel. It was intended for use in supercomputers, servers, and high-end workstations. Its architecture allowed use of standard programming languages and application programming interfaces (APIs) such as OpenMP. Xeon Phi launched in 2010. Since it was originally based on an earlier GPU design ( codenamed "Larrabee") by Intel that was cancelled in 2009, it shared application areas with GPUs. The main difference between Xeon Phi and a GPGPU like Nvidia Tesla was that Xeon Phi, with an x86-compatible core, could, with less modification, run software that was originally targeted to a standard x86 CPU. Initially in the form of PCI Express-based add-on cards, a second-generation product, codenamed ''Knights Landing'', was announced in June 2013. These second-generation chips could be used as a standalone CPU, rather than just as an add-in card. In June 2013, the Tianhe-2 supercomputer at the National S ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Skylake (microarchitecture)

Skylake is Intel's codename for its sixth generation Core microprocessor family that was launched on August 5, 2015, succeeding the Broadwell microarchitecture. Skylake is a microarchitecture redesign using the same 14 nm manufacturing process technology as its predecessor, serving as a tock in Intel's tick–tock manufacturing and design model. According to Intel, the redesign brings greater CPU and GPU performance and reduced power consumption. Skylake CPUs share their microarchitecture with Kaby Lake, Coffee Lake, Whiskey Lake, and Comet Lake CPUs. Skylake is the last Intel platform on which Windows earlier than Windows 10 are officially supported by Microsoft, although enthusiast-created modifications are available that disabled the Windows Update check and allowed Windows 8.1 and earlier to continue to receive Windows Updates on this and later platforms. Some of the processors based on the Skylake microarchitecture are marketed as sixth-generation Core. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Alder Lake

Alder Lake is Intel's codename for the 12th generation of Intel Core processors based on a hybrid architecture utilizing Golden Cove performance cores and Gracemont efficient cores. It is fabricated using Intel's Intel 7 process, previously referred to as Intel 10 nm Enhanced SuperFin (10ESF). The 10ESF has a 10%-15% boost in performance over the 10SF used in the mobile Tiger Lake processors. Intel officially announced 12th Gen Intel Core CPUs on October 27, 2021, mobile CPUs and non-K series desktop CPUs on January 4, 2022, Alder Lake-P and -U series on February 23, 2022, and Alder Lake-HX series on May 10, 2022. History It was announced in November 2021 that Intel Alder Lake would use a hybrid architecture combining performance and efficiency cores, similar to ARM big.LITTLE. This was Intel's second hybrid architecture, after the mobile-only Lakefield released in June 2020. While the desktop Alder Lake processors were already on the market by January 2022, the mo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SIMD

Single instruction, multiple data (SIMD) is a type of parallel computer, parallel processing in Flynn's taxonomy. SIMD describes computers with multiple processing elements that perform the same operation on multiple data points simultaneously. SIMD can be internal (part of the hardware design) and it can be directly accessible through an instruction set architecture (ISA), but it should not be confused with an ISA. Such machines exploit Data parallelism, data level parallelism, but not Concurrent computing, concurrency: there are simultaneous (parallel) computations, but each unit performs exactly the same instruction at any given moment (just with different data). A simple example is to add many pairs of numbers together, all of the SIMD units are performing an addition, but each one has different pairs of values to add. SIMD is particularly applicable to common tasks such as adjusting the contrast in a digital image or adjusting the volume of digital audio. Most modern Cen ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cannon Lake (microarchitecture)

Cannon Lake is list of Intel codenames, Intel's codename for the ninth generation of Intel Core, Core processors based on Palm Cove, a 10 nm process, 10 nm die shrink of the Kaby Lake microarchitecture. As a die shrink, Palm Cove is a new ''process'' in Intel's Process–architecture–optimization model, process-architecture-optimization execution plan as the next step in semiconductor fabrication. Cannon Lake CPUs are the first mainstream CPUs to include the AVX-512 instruction set. Prior to Cannon Lake's launch, Intel launched another 14 nm process refinement with the codename Coffee Lake. The successor of Cannon Lake is Ice Lake (microarchitecture), Ice Lake, powered by the Sunny Cove (microarchitecture), Sunny Cove microarchitecture, which represents the ''architecture'' phase in the ''process-architecture-optimization'' model. Design history and features Cannon Lake was initially expected to be released in 2015/2016, but the release was pushed back to 2018. Inte ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Gather-scatter

Gather/scatter is a type of memory addressing that at once collects (gathers) from, or stores (scatters) data to, multiple, arbitrary memory indices. Examples of its use include sparse linear algebra operations, sorting algorithms, fast Fourier transforms, and some computational graph theory problems. It is the vector equivalent of register indirect addressing, with gather involving indexed reads, and scatter, indexed writes. Vector processors (and some SIMD units in CPUs) have hardware support for gather and scatter operations, as do many input/output systems, allowing large data sets to be transferred to main memory more rapidly. The concept is somewhat similar to vectored I/O, which is sometimes also referred to as scatter-gather I/O. This system differs in that it is used to map multiple sources of data from contiguous structures into a single stream for reading or writing. A common example is writing out a series of strings, which in most programming languages would be st ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sapphire Rapids

Sapphire Rapids is a codename for Intel's server (fourth generation Xeon Scalable) and workstation (Xeon W-2400/2500 and Xeon W-3400/3500) processors based on the Golden Cove microarchitecture and produced using Intel 7. It features up to 60 cores and an array of accelerators, and it is the first generation of Intel server and workstation processors to use a chiplet design. Sapphire Rapids is part of the Eagle Stream server platform. In addition, it powers Aurora, an exascale supercomputer in the United States, at Argonne National Laboratory. History Sapphire Rapids has been a long-standing Intel project along Alder Lake in development for over five years and has been subjected to many delays. It was first announced by Intel at their Investor Meeting in May 2019 with the intention of Sapphire Rapids succeeding Ice Lake and Cooper Lake in 2021. Intel again announced details on Sapphire Rapids in their August 2021 Architecture Day presentation with no mention of a launch ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

EVEX Prefix

The EVEX prefix (enhanced vector extension) and corresponding coding scheme is an extension to the 32-bit x86 (IA-32) and 64-bit x86-64 (AMD64) instruction set architecture. EVEX is based on, but should not be confused with the MVEX prefix used by the Knights Corner processor. The EVEX scheme is a 4-byte extension to the VEX scheme which supports the AVX-512 instruction set and allows addressing new 512-bit ZMM registers and new 64-bit operand mask registers. With Advanced Performance Extensions, the Extended EVEX prefix redefines the semantics of several payload bits. Features EVEX coding can address 8 operand mask registers, 16 general-purpose registers and 32 vector registers in 64-bit mode (otherwise, 8 general-purpose and 8 vector), and can support up to 4 operands. Like the VEX coding scheme, the EVEX prefix unifies existing opcode prefixes and escape codes, memory addressing and operand length modifiers of the x86 instruction set. The following features are carried over ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Streaming SIMD Extensions

In computing, Streaming SIMD Extensions (SSE) is a single instruction, multiple data ( SIMD) instruction set extension to the x86 architecture, designed by Intel and introduced in 1999 in its Pentium III series of central processing units (CPUs) shortly after the appearance of Advanced Micro Devices (AMD's) 3DNow!. SSE contains 70 new instructions (65 unique mnemonics using 70 encodings), most of which work on single precision floating-point data. SIMD instructions can greatly increase performance when exactly the same operations are to be performed on multiple data objects. Typical applications are digital signal processing and graphics processing. Intel's first IA-32 SIMD effort was the MMX instruction set. MMX had two main problems: it re-used existing x87 floating-point registers making the CPUs unable to work on both floating-point and SIMD data at the same time, and it only worked on integers. SSE floating-point instructions operate on a new independent register s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Larrabee (microarchitecture)

Larrabee is the codename for a cancelled GPGPU chip that Intel was developing separately from its current line of integrated graphics accelerators. It is named after either Mount Larrabee or Larrabee State Park in the state of Washington. The chip was to be released in 2010 as the core of a consumer 3D graphics card, but these plans were cancelled due to delays and disappointing early performance figures. The project to produce a GPU retail product directly from the Larrabee research project was terminated in May 2010 and its technology was passed on to the Xeon Phi. The Intel MIC multiprocessor architecture announced in 2010 inherited many design elements from the Larrabee project, but does not function as a graphics processing unit; the product is intended as a co-processor for high performance computing. Almost a decade later, on June 12, 2018; the idea of an Intel dedicated GPU was revived again with Intel's desire to create a discrete GPU by 2020. This project would eventu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Array Programming

In computer science, array programming refers to solutions that allow the application of operations to an entire set of values at once. Such solutions are commonly used in computational science, scientific and engineering settings. Modern programming languages that support array programming (also known as vector (data structure), vector or multidimensional analysis, multidimensional languages) have been engineered specifically to generalize operations on scalar (computing), scalars to apply transparently to vector (geometric), vectors, matrix (mathematics), matrices, and higher-dimensional arrays. These include APL (programming language), APL, J (programming language), J, Fortran, MATLAB, Analytica (software), Analytica, GNU Octave, Octave, R (programming language), R, Cilk Plus, Julia (programming language), Julia, Perl Data Language, Perl Data Language (PDL), Raku (programming language). In these languages, an operation that operates on entire arrays can be called a ''vectorized' ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |