POWER2 on:

[Wikipedia]

[Google]

[Amazon]

The POWER2, originally named RIOS2, is a

An improved version of the POWER2 optimized for

An improved version of the POWER2 optimized for

''POWER2 Super Chip'' (P2SC) was released in October 1996 as the successor of the POWER2. It was a single-chip implementation of the eight-chip POWER2, integrating 15 million transistors on a 335 mm2 die manufactured in IBM's 0.29 μm five-layer metal CMOS-6S process. The first version ran at 120 or 135 MHz, nearly twice as fast as the POWER2 at 71.5 MHz, with the memory and I/O buses running at half speed to support the higher clock frequency. IBM claimed that the performance of this version was 5.5 SPECint95_base and 14.5 SPECfp95_base. A faster 160 MHz part fabricated in the 0.25 μm CMOS-6S2 process was announced at the Microprocessor Forum in October 1997.

The P2SC was not a complete copy of the POWER2, the L1 data cache and data

''POWER2 Super Chip'' (P2SC) was released in October 1996 as the successor of the POWER2. It was a single-chip implementation of the eight-chip POWER2, integrating 15 million transistors on a 335 mm2 die manufactured in IBM's 0.29 μm five-layer metal CMOS-6S process. The first version ran at 120 or 135 MHz, nearly twice as fast as the POWER2 at 71.5 MHz, with the memory and I/O buses running at half speed to support the higher clock frequency. IBM claimed that the performance of this version was 5.5 SPECint95_base and 14.5 SPECfp95_base. A faster 160 MHz part fabricated in the 0.25 μm CMOS-6S2 process was announced at the Microprocessor Forum in October 1997.

The P2SC was not a complete copy of the POWER2, the L1 data cache and data

"IBM readies RISC Progeny in Unix"

'' Electronic News''. * Shippy, David (9 August 1994). "The Power2+ Processor". '' Hot Chips 6''. * * Statt, Paul (January 1994). "Power2 Takes the Lead--For Now". ''

processor

Processor may refer to:

Computing Hardware

* Processor (computing)

**Central processing unit (CPU), the hardware within a computer that executes a program

*** Microprocessor, a central processing unit contained on a single integrated circuit (I ...

designed by IBM that implemented the POWER

Power most often refers to:

* Power (physics), meaning "rate of doing work"

** Engine power, the power put out by an engine

** Electric power

* Power (social and political), the ability to influence people or events

** Abusive power

Power may a ...

instruction set architecture

In computer science, an instruction set architecture (ISA), also called computer architecture, is an abstract model of a computer. A device that executes instructions described by that ISA, such as a central processing unit (CPU), is called an ...

. The POWER2 was the successor of the POWER1, debuting in September 1993 within IBM's RS/6000

The RISC System/6000 (RS/6000) is a family of Reduced instruction set computer, RISC-based Unix Server (computing), servers, workstations and supercomputers made by IBM in the 1990s. The RS/6000 family replaced the IBM RT PC computer platform in ...

systems. When introduced, the POWER2 was the fastest microprocessor, surpassing the Alpha 21064

The Alpha 21064 is a microprocessor developed and fabricated by Digital Equipment Corporation that implemented the Alpha (introduced as the Alpha AXP) instruction set architecture (ISA). It was introduced as the DECchip 21064 before it was renam ...

. When the Alpha 21064A was introduced in 1993, the POWER2 lost the lead and became second. IBM claimed that the performance for a 62.5 MHz POWER2 was 73.3 SPECint92 and 134.6 SPECfp92.

The open source GCC compiler removed support for POWER1 (RIOS) and POWER2 (RIOS2) in the 4.5 release.

Description

Improvements over the POWER1 included enhancements to the POWER instruction set architecture (consisting of new user and system instructions and other system-related features), higher clock rates (55 to 71.5 MHz), an extra fixed point unit andfloating point unit

Floating may refer to:

* a type of dental work performed on horse teeth

* use of an isolation tank

* the guitar-playing technique where chords are sustained rather than scratched

* ''Floating'' (play), by Hugh Hughes

* Floating (psychological ...

, a larger 32 KB instruction cache, and a larger 128 or 256 KB data cache. The POWER2 was a multi-chip design consisting of six or eight semi-custom integrated circuits, depending on the amount of data cache (the 256 KB configuration required eight chips). The partitioning of the design was identical to that of the POWER1: an instruction cache unit chip, a fixed-point unit chip, a floating-point unit chip, a storage control unit chip, and two or four data cache unit chips.

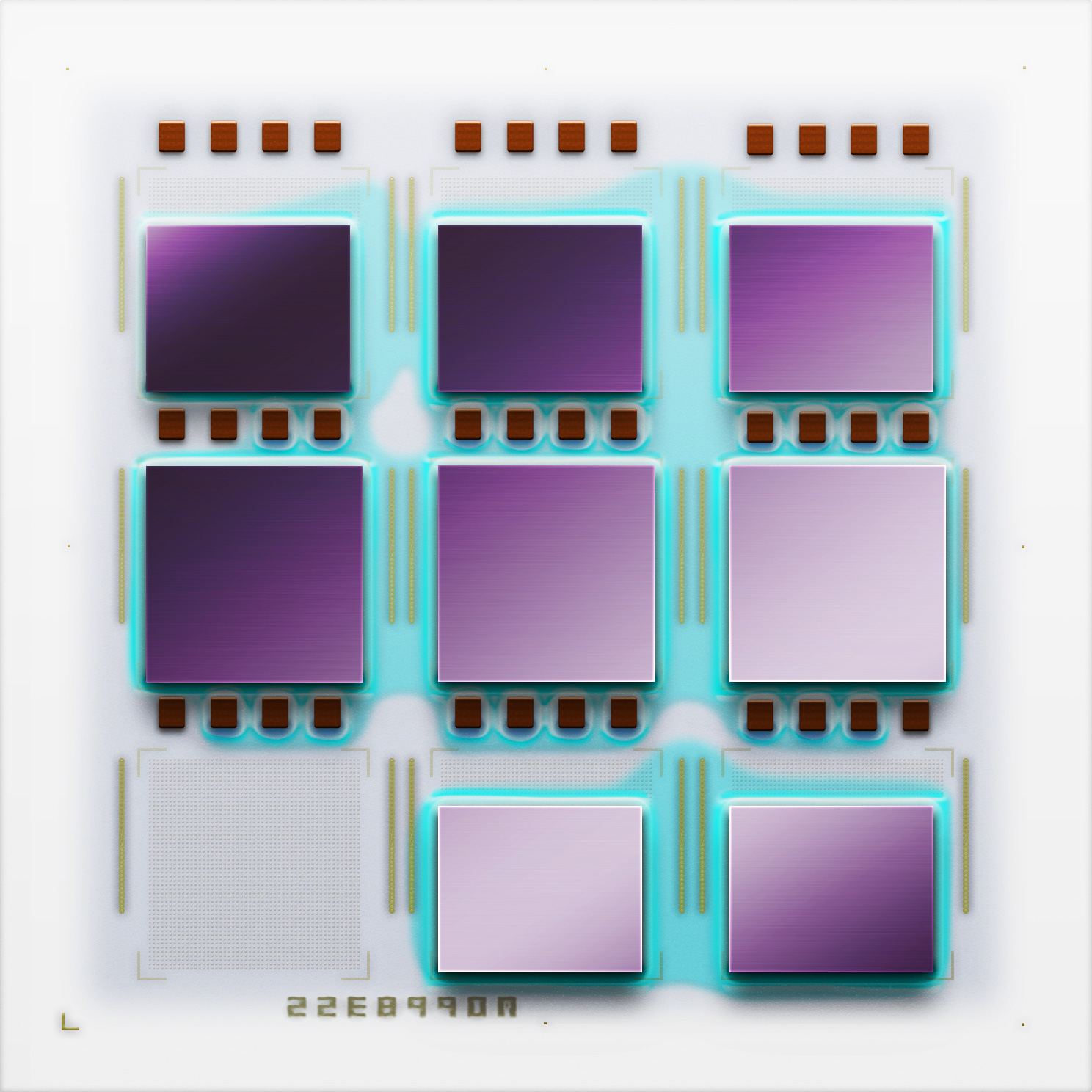

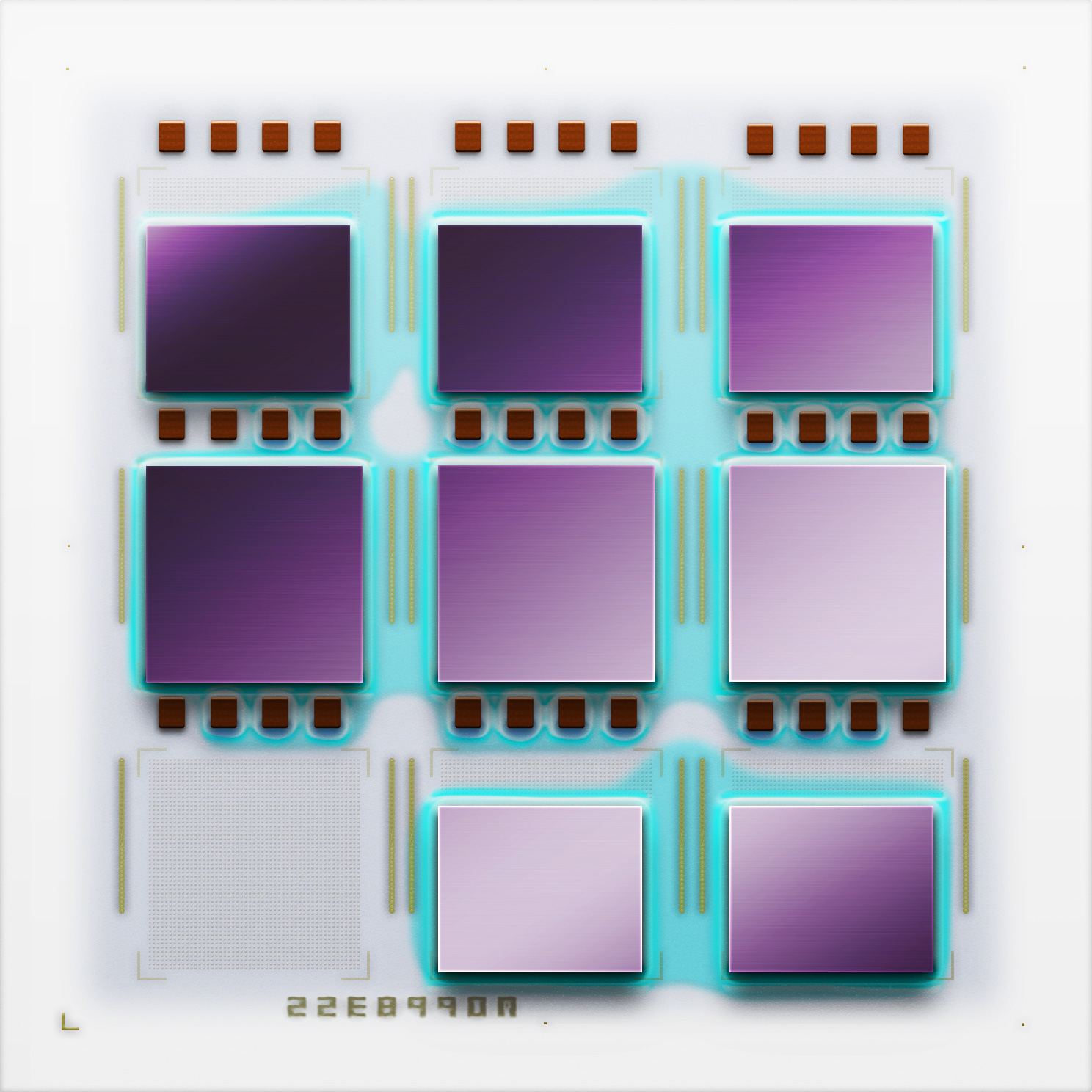

The eight-chip configuration contains a total of 23 million transistors and a total die area of 1,215 mm2. The chips are manufactured by IBM in its 0.72 μm CMOS process, which features a 0.45 μm effective channel length; and one layer of polysilicon and four layers of metal interconnect. The chips are packaged in a ceramic multi-chip module

A multi-chip module (MCM) is generically an electronic assembly (such as a package with a number of conductor terminals or "pins") where multiple integrated circuits (ICs or "chips"), semiconductor dies and/or other discrete components are in ...

(MCM) that measures 64 mm by 64 mm.

POWER2+

An improved version of the POWER2 optimized for

An improved version of the POWER2 optimized for transaction processing

Transaction processing is information processing in computer science that is divided into individual, indivisible operations called ''transactions''. Each transaction must succeed or fail as a complete unit; it can never be only partially compl ...

was introduced in May 1994 as the POWER2+. Transaction processing workloads benefited from the addition of a L2 cache with capacities of 512 KB, 1 MB and 2 MB. This cache was implemented off-package with industry-standard burst SRAMs. The cache was connected to the POWER2+ via a 64- (for low-end systems) or 128-bit bus (for high-end systems). The cache was direct-mapped, had a 128-byte line size, and was write-through

In computing, a cache ( ) is a hardware or software component that stores data so that future requests for that data can be served faster; the data stored in a cache might be the result of an earlier computation or a copy of data stored elsewhe ...

. The cache tags were contained on the storage control unit chip. The POWER2+ has a narrower 64- or 128-bit memory bus and a smaller 64 or 128 KB data cache. As there is less cache, the data cache unit chips are smaller as a result, and the revised storage control unit chip is also smaller. A goal for the six-chip configuration was to reduce cost, and therefore the chips are packaged in a solder ball connect (SBC) package instead of a MCM.

POWER2 Super Chip (P2SC)

''POWER2 Super Chip'' (P2SC) was released in October 1996 as the successor of the POWER2. It was a single-chip implementation of the eight-chip POWER2, integrating 15 million transistors on a 335 mm2 die manufactured in IBM's 0.29 μm five-layer metal CMOS-6S process. The first version ran at 120 or 135 MHz, nearly twice as fast as the POWER2 at 71.5 MHz, with the memory and I/O buses running at half speed to support the higher clock frequency. IBM claimed that the performance of this version was 5.5 SPECint95_base and 14.5 SPECfp95_base. A faster 160 MHz part fabricated in the 0.25 μm CMOS-6S2 process was announced at the Microprocessor Forum in October 1997.

The P2SC was not a complete copy of the POWER2, the L1 data cache and data

''POWER2 Super Chip'' (P2SC) was released in October 1996 as the successor of the POWER2. It was a single-chip implementation of the eight-chip POWER2, integrating 15 million transistors on a 335 mm2 die manufactured in IBM's 0.29 μm five-layer metal CMOS-6S process. The first version ran at 120 or 135 MHz, nearly twice as fast as the POWER2 at 71.5 MHz, with the memory and I/O buses running at half speed to support the higher clock frequency. IBM claimed that the performance of this version was 5.5 SPECint95_base and 14.5 SPECfp95_base. A faster 160 MHz part fabricated in the 0.25 μm CMOS-6S2 process was announced at the Microprocessor Forum in October 1997.

The P2SC was not a complete copy of the POWER2, the L1 data cache and data translation lookaside buffer

A translation lookaside buffer (TLB) is a memory cache that stores the recent translations of virtual memory to physical memory. It is used to reduce the time taken to access a user memory location. It can be called an address-translation cache ...

(TLB) capacities were halved to 128 KB and 256 entries, respectively, and a rarely used feature that locked entries in the TLB was not implemented in order to fit the original design onto a single die.

The P2SC was succeeded by the POWER3

The POWER3 is a microprocessor, designed and exclusively manufactured by IBM, that implemented the 64-bit version of the PowerPC instruction set architecture (ISA), including all of the optional instructions of the ISA (at the time) such as ...

as IBM's flagship microprocessor on the RS/6000

The RISC System/6000 (RS/6000) is a family of Reduced instruction set computer, RISC-based Unix Server (computing), servers, workstations and supercomputers made by IBM in the 1990s. The RS/6000 family replaced the IBM RT PC computer platform in ...

line in 1998. A notable use of the P2SC was the 30-node IBM Deep Blue supercomputer that beat world champion Garry Kasparov

Garry Kimovich Kasparov (born 13 April 1963) is a Russian chess grandmaster, former World Chess Champion, writer, political activist and commentator. His peak rating of 2851, achieved in 1999, was the highest recorded until being surpassed by ...

at chess in 1997. However, the computer's chess-playing capabilities were a result of its expert system

In artificial intelligence, an expert system is a computer system emulating the decision-making ability of a human expert.

Expert systems are designed to solve complex problems by reasoning through bodies of knowledge, represented mainly as if� ...

running on custom VLSI chips, rather than the P2SCs.

See also

* IBM POWER Instruction Set Architecture *IBM Power microprocessors

IBM Power microprocessors (originally POWER prior to Power10) are designed and sold by IBM for servers and supercomputers. The name "POWER" was originally presented as an acronym for "Performance Optimization With Enhanced RISC". The Power ...

* POWER1

* POWER3

The POWER3 is a microprocessor, designed and exclusively manufactured by IBM, that implemented the 64-bit version of the PowerPC instruction set architecture (ISA), including all of the optional instructions of the ISA (at the time) such as ...

Notes

References

* * Ball, Richard (15 October 1997). "Chipville USA". ''Electronics Weekly

''Electronics Weekly'' is a weekly trade journal for electronics professionals which was first published by Reed Business Information on 7 September 1960. It was the first British Electronics newspaper and its founding editor was Cyril C. Gee who ...

''.

* DeTar, Jim (22 August 1994). "IBM details Power2+; DEC bares new Alpha AXP". '' Electronic News''.

* Gwennap, Linley (4 October 1993). "IBM Regains Performance Lead with Power2". ''Microprocessor Report

''Microprocessor Report'' is a newsletter covering the microprocessor industry. The publication is accessible only to paying subscribers. To avoid bias, it does not take advertisements.

The publication provides extensive analysis of new high-perfo ...

''.

* Gwennap, Linley (26 August 1996). "IBM Crams POWER2 onto Single Chip". ''Microprocessor Report

''Microprocessor Report'' is a newsletter covering the microprocessor industry. The publication is accessible only to paying subscribers. To avoid bias, it does not take advertisements.

The publication provides extensive analysis of new high-perfo ...

''.

*

* Lineback, J. Robert (28 June 1993)"IBM readies RISC Progeny in Unix"

'' Electronic News''. * Shippy, David (9 August 1994). "The Power2+ Processor". '' Hot Chips 6''. * * Statt, Paul (January 1994). "Power2 Takes the Lead--For Now". ''

Byte

The byte is a unit of digital information that most commonly consists of eight bits. Historically, the byte was the number of bits used to encode a single character of text in a computer and for this reason it is the smallest addressable uni ...

''.

*

Further reading

* {{mdash Chapter 6 describes the POWER2 architecture and processor IBM microprocessors Computer-related introductions in 1993 Superscalar microprocessors 32-bit microprocessors