Latch-up on:

[Wikipedia]

[Google]

[Amazon]

A latch-up is a type of  Another common cause of latch-ups is ionizing radiation which makes this a significant issue in electronic products designed for space (or very high-altitude) applications. A single event latch-up is a latch-up caused by a single event upset, typically heavy ions or protons from cosmic rays or solar flares.

Single-event latchup (SEL) can be completely eliminated by several manufacturing techniques, as part of radiation hardening.

High-power microwave interference can also trigger latch ups.

Both CMOS integrated circuits and TTL integrated circuits are more susceptible to latch-up at higher temperatures.

Another common cause of latch-ups is ionizing radiation which makes this a significant issue in electronic products designed for space (or very high-altitude) applications. A single event latch-up is a latch-up caused by a single event upset, typically heavy ions or protons from cosmic rays or solar flares.

Single-event latchup (SEL) can be completely eliminated by several manufacturing techniques, as part of radiation hardening.

High-power microwave interference can also trigger latch ups.

Both CMOS integrated circuits and TTL integrated circuits are more susceptible to latch-up at higher temperatures.

All CMOS ICs have latch-up paths, but there are several design techniques that reduce susceptibility to latch-up.

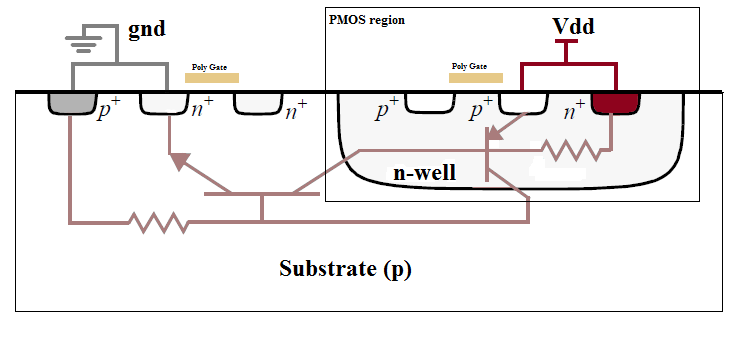

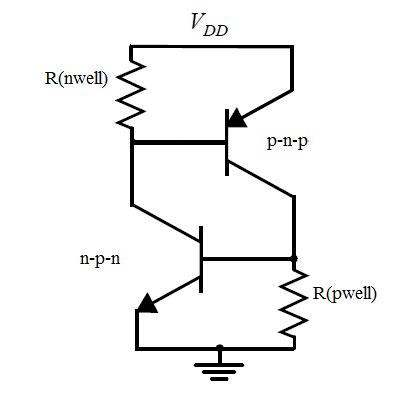

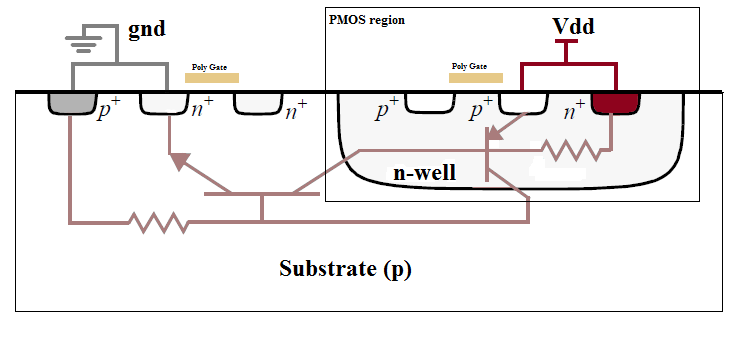

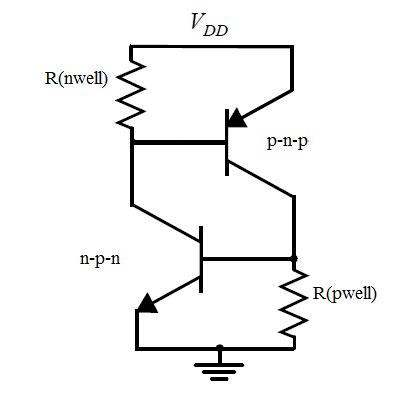

In CMOS technology, there are a number of intrinsic bipolar junction transistors. In CMOS processes, these transistors can create problems when the combination of n-well/p-well and substrate results in the formation of parasitic n-p-n-p structures. Triggering these thyristor-like devices leads to a shorting of the Vdd and GND lines, usually resulting in destruction of the chip, or a system failure that can only be resolved by power-down.

Consider the n-well structure in the first figure. The n-p-n-p structure is formed by the source of the NMOS, the p-substrate, the n-well and the source of the PMOS. A circuit equivalent is also shown. When one of the two bipolar transistors gets forward biased (due to current flowing through the well, or substrate), it feeds the base of the other transistor. This positive feedback increases the current until the circuit fails or burns out.

The invention of the now industry-standard technique to prevent CMOS latch-up was made by Hughes Aircraft company in 1977.

All CMOS ICs have latch-up paths, but there are several design techniques that reduce susceptibility to latch-up.

In CMOS technology, there are a number of intrinsic bipolar junction transistors. In CMOS processes, these transistors can create problems when the combination of n-well/p-well and substrate results in the formation of parasitic n-p-n-p structures. Triggering these thyristor-like devices leads to a shorting of the Vdd and GND lines, usually resulting in destruction of the chip, or a system failure that can only be resolved by power-down.

Consider the n-well structure in the first figure. The n-p-n-p structure is formed by the source of the NMOS, the p-substrate, the n-well and the source of the PMOS. A circuit equivalent is also shown. When one of the two bipolar transistors gets forward biased (due to current flowing through the well, or substrate), it feeds the base of the other transistor. This positive feedback increases the current until the circuit fails or burns out.

The invention of the now industry-standard technique to prevent CMOS latch-up was made by Hughes Aircraft company in 1977.

This standard is commonly referenced in IC wikt:qualification, qualification specifications.

Latch-up in CMOS designs

* [https://web.archive.org/web/20120312074109/http://www.maxwell.com/products/microelectronics/latchup-protection Maxwell Technologies Microelectronics: Latchup Protection Technology]

SCR Latchup Video Tutorial

Integrated circuits Semiconductor device defects

short circuit

A short circuit (sometimes abbreviated to short or s/c) is an electrical circuit that allows a current to travel along an unintended path with no or very low electrical impedance. This results in an excessive current flowing through the circui ...

which can occur in an integrated circuit (IC). More specifically it is the inadvertent creation of a low- impedance path between the power supply rails of a MOSFET circuit, triggering a parasitic structure

In a semiconductor device, a parasitic structure is a portion of the device that resembles in structure some other, simpler semiconductor device, and causes the device to enter an unintended mode of operation when subjected to conditions outside ...

which disrupts proper functioning of the part, possibly even leading to its destruction due to overcurrent. A power cycle is required to correct this situation.

The parasitic structure is usually equivalent to a thyristor

A thyristor () is a solid-state semiconductor device with four layers of alternating P- and N-type materials used for high-power applications. It acts exclusively as a bistable switch (or a latch), conducting when the gate receives a current ...

(or SCR), a PNPN structure which acts as a PNP and an NPN transistor

upright=1.4, gate (G), body (B), source (S) and drain (D) terminals. The gate is separated from the body by an insulating layer (pink).

A transistor is a semiconductor device used to Electronic amplifier, amplify or electronic switch, switch ...

stacked next to each other. During a latch-up when one of the transistors is conducting, the other one begins conducting too. They both keep each other in saturation for as long as the structure is forward-biased and some current flows through it - which usually means until a power-down. The SCR parasitic structure is formed as a part of the totem-pole PMOS and NMOS transistor pair on the output drivers of the gates.

The latch-up does not have to happen between the power rails - it can happen at any place where the required parasitic structure exists. A common cause of latch-up is a positive or negative voltage spike on an input or output pin of a digital chip that exceeds the rail voltage by more than a diode drop. Another cause is the supply voltage exceeding the absolute maximum rating, often from a transient spike

Spike, spikes, or spiking may refer to:

Arts, entertainment, and media

Books

* ''The Spike'' (novel), a novel by Arnaud de Borchgrave

* ''The Spike'' (book), a nonfiction book by Damien Broderick

* ''The Spike'', a starship in Peter F. Hamilto ...

in the power supply. It leads to a breakdown

Breakdown may refer to:

Breaking down

*Breakdown (vehicle), failure of a motor vehicle in such a way that it cannot be operated

*Chemical decomposition, also called chemical breakdown, the breakdown of a substance into simpler components

*Decompo ...

of an internal P-n junction, junction. This frequently happens in circuits which use multiple supply voltages that do not come up in the required sequence on power-up, leading to voltages on data lines exceeding the input rating of parts that have not yet reached a nominal supply voltage. Latch-ups can also be caused by an electrostatic discharge event.

Another common cause of latch-ups is ionizing radiation which makes this a significant issue in electronic products designed for space (or very high-altitude) applications. A single event latch-up is a latch-up caused by a single event upset, typically heavy ions or protons from cosmic rays or solar flares.

Single-event latchup (SEL) can be completely eliminated by several manufacturing techniques, as part of radiation hardening.

High-power microwave interference can also trigger latch ups.

Both CMOS integrated circuits and TTL integrated circuits are more susceptible to latch-up at higher temperatures.

Another common cause of latch-ups is ionizing radiation which makes this a significant issue in electronic products designed for space (or very high-altitude) applications. A single event latch-up is a latch-up caused by a single event upset, typically heavy ions or protons from cosmic rays or solar flares.

Single-event latchup (SEL) can be completely eliminated by several manufacturing techniques, as part of radiation hardening.

High-power microwave interference can also trigger latch ups.

Both CMOS integrated circuits and TTL integrated circuits are more susceptible to latch-up at higher temperatures.

CMOS latch-up

All CMOS ICs have latch-up paths, but there are several design techniques that reduce susceptibility to latch-up.

In CMOS technology, there are a number of intrinsic bipolar junction transistors. In CMOS processes, these transistors can create problems when the combination of n-well/p-well and substrate results in the formation of parasitic n-p-n-p structures. Triggering these thyristor-like devices leads to a shorting of the Vdd and GND lines, usually resulting in destruction of the chip, or a system failure that can only be resolved by power-down.

Consider the n-well structure in the first figure. The n-p-n-p structure is formed by the source of the NMOS, the p-substrate, the n-well and the source of the PMOS. A circuit equivalent is also shown. When one of the two bipolar transistors gets forward biased (due to current flowing through the well, or substrate), it feeds the base of the other transistor. This positive feedback increases the current until the circuit fails or burns out.

The invention of the now industry-standard technique to prevent CMOS latch-up was made by Hughes Aircraft company in 1977.

All CMOS ICs have latch-up paths, but there are several design techniques that reduce susceptibility to latch-up.

In CMOS technology, there are a number of intrinsic bipolar junction transistors. In CMOS processes, these transistors can create problems when the combination of n-well/p-well and substrate results in the formation of parasitic n-p-n-p structures. Triggering these thyristor-like devices leads to a shorting of the Vdd and GND lines, usually resulting in destruction of the chip, or a system failure that can only be resolved by power-down.

Consider the n-well structure in the first figure. The n-p-n-p structure is formed by the source of the NMOS, the p-substrate, the n-well and the source of the PMOS. A circuit equivalent is also shown. When one of the two bipolar transistors gets forward biased (due to current flowing through the well, or substrate), it feeds the base of the other transistor. This positive feedback increases the current until the circuit fails or burns out.

The invention of the now industry-standard technique to prevent CMOS latch-up was made by Hughes Aircraft company in 1977.

Preventing latch-up

It is possible to design chips to be resistant to latch-up by adding a layer of insulating oxide (called a ''trench'') that surrounds both the NMOS and the PMOS transistors. This breaks the parasitic silicon-controlled rectifier (SCR) structure between these transistors. Such parts are important in the cases where the proper sequencing of power and signals cannot be guaranteed, such as hot swap devices. Devices fabricated in lightly doped epitaxial layers grown on heavily doped substrates are also less susceptible to latch-up. The heavily doped layer acts as a current sink where excess minority carriers can quickly recombine.Stephen A. Campbell, The Science and Engineering of Microelectronic Fabrication, Oxford University Press (Indian Edition 2007) p.461 Most silicon on insulator, silicon-on-insulator devices are inherently latch-up-resistant. Latch-up is the low resistance connection between tub and power supply rails. Also to avoid the latch, a separate tap connection is put for each transistor. But this will increase the size of the device so fabs give a minimum space to put a tap, for example, 10 μm in 130 nm technology.Testing for latch-up

* See Electronic Industries Alliance, EIA/JEDEC STANDARD IC Latch-Up Test EIA/JESD78.This standard is commonly referenced in IC wikt:qualification, qualification specifications.

References

{{ReflistExternal links

Latch-up in CMOS designs

* [https://web.archive.org/web/20120312074109/http://www.maxwell.com/products/microelectronics/latchup-protection Maxwell Technologies Microelectronics: Latchup Protection Technology]

SCR Latchup Video Tutorial

Integrated circuits Semiconductor device defects