Infinity Fabric on:

[Wikipedia]

[Google]

[Amazon]

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer

similar to high end Solid-state drive#Standard card form factors, PCIe SSDs ULLtraDIMM flash RAM) technology—a wider range of RAM speeds on a common CPU bus than any Intel front-side bus. Intel technologies require each speed range of RAM to have its own interface, resulting in a more complex motherboard layout but with fewer bottlenecks. HTX 3.1 at 26 GB/s can serve as a unified bus for as many as four DDR4 sticks running at the fastest proposed speeds. Beyond that DDR4 RAM may require two or more HTX 3.1 buses diminishing its value as unified transport.

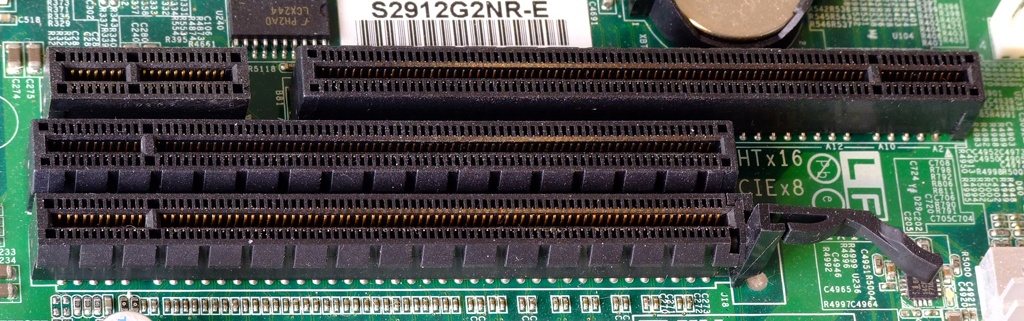

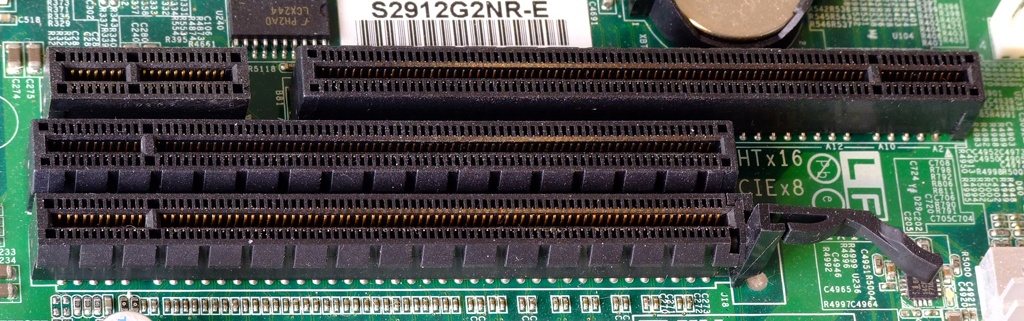

A connector specification that allows a slot-based peripheral to have direct connection to a microprocessor using a HyperTransport interface was released by the HyperTransport Consortium. It is known as HyperTransport eXpansion (HTX). Using a reversed instance of the same mechanical connector as a 16-lane

A connector specification that allows a slot-based peripheral to have direct connection to a microprocessor using a HyperTransport interface was released by the HyperTransport Consortium. It is known as HyperTransport eXpansion (HTX). Using a reversed instance of the same mechanical connector as a 16-lane

* AMD

processor

Processor may refer to:

Computing Hardware

* Processor (computing)

**Central processing unit (CPU), the hardware within a computer that executes a program

*** Microprocessor, a central processing unit contained on a single integrated circuit (I ...

s. It is a bidirectional serial/parallel

Parallel is a geometric term of location which may refer to:

Computing

* Parallel algorithm

* Parallel computing

* Parallel metaheuristic

* Parallel (software), a UNIX utility for running programs in parallel

* Parallel Sysplex, a cluster o ...

high-bandwidth

Bandwidth commonly refers to:

* Bandwidth (signal processing) or ''analog bandwidth'', ''frequency bandwidth'', or ''radio bandwidth'', a measure of the width of a frequency range

* Bandwidth (computing), the rate of data transfer, bit rate or thr ...

, low- latency point-to-point link

In telecommunications, a point-to-point connection refers to a communications connection between two communication endpoints or nodes. An example is a telephone call, in which one telephone is connected with one other, and what is said by one c ...

that was introduced on April 2, 2001. The HyperTransport Consortium {{Short description, Body responsible for regulating and promoting the HyperTransport technology

The HyperTransport Consortium is an industry consortium responsible for specifying and promoting the computer bus technology called HyperTransport.

O ...

is in charge of promoting and developing HyperTransport technology.

HyperTransport is best known as the system bus

A system bus is a single computer bus that connects the major components of a computer system,

combining the functions of a data bus to carry information, an address bus to determine where it should be sent or read from, and a control bus to det ...

architecture of AMD central processing unit

A central processing unit (CPU), also called a central processor, main processor or just processor, is the electronic circuitry that executes instructions comprising a computer program. The CPU performs basic arithmetic, logic, controlling, a ...

s (CPUs) from Athlon 64

The Athlon 64 is a ninth-generation, AMD64-architecture microprocessor produced by Advanced Micro Devices (AMD), released on September 23, 2003. It is the third processor to bear the name ''Athlon'', and the immediate successor to the Athlon XP. T ...

through AMD FX and the associated motherboard

A motherboard (also called mainboard, main circuit board, mb, mboard, backplane board, base board, system board, logic board (only in Apple computers) or mobo) is the main printed circuit board (PCB) in general-purpose computers and other expand ...

chipsets. HyperTransport has also been used by IBM and Apple

An apple is an edible fruit produced by an apple tree (''Malus domestica''). Apple trees are cultivated worldwide and are the most widely grown species in the genus '' Malus''. The tree originated in Central Asia, where its wild ancest ...

for the Power Mac G5 machines, as well as a number of modern MIPS systems.

The current specification HTX 3.1 remained competitive for 2014 high-speed (2666 and 3200 MT/s or about 10.4 GB/s and 12.8 GB/s) DDR4

Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) is a type of synchronous dynamic random-access memory with a high bandwidth (" double data rate") interface.

Released to the market in 2014, it is a variant of dynamic ran ...

RAM and slower (around 1 GB/similar to high end Solid-state drive#Standard card form factors, PCIe SSDs ULLtraDIMM flash RAM) technology—a wider range of RAM speeds on a common CPU bus than any Intel front-side bus. Intel technologies require each speed range of RAM to have its own interface, resulting in a more complex motherboard layout but with fewer bottlenecks. HTX 3.1 at 26 GB/s can serve as a unified bus for as many as four DDR4 sticks running at the fastest proposed speeds. Beyond that DDR4 RAM may require two or more HTX 3.1 buses diminishing its value as unified transport.

Overview

Links and rates

HyperTransport comes in four versions—1.x, 2.0, 3.0, and 3.1—which run from 200 MHz to 3.2 GHz. It is also a DDR or "double data rate

In computing, a computer bus operating with double data rate (DDR) transfers data on both the rising and falling edges of the clock signal. This is also known as double pumped, dual-pumped, and double transition. The term toggle mode is used in ...

" connection, meaning it sends data on both the rising and falling edges of the clock signal

In electronics and especially synchronous digital circuits, a clock signal (historically also known as ''logic beat'') oscillates between a high and a low state and is used like a metronome to coordinate actions of digital circuits.

A clock si ...

. This allows for a maximum data rate of 6400 MT/s when running at 3.2 GHz. The operating frequency is autonegotiated with the motherboard chipset (North Bridge) in current computing.

HyperTransport supports an autonegotiated bit width, ranging from 2 to 32 bits per link; there are two unidirectional links per HyperTransport bus. With the advent of version 3.1, using full 32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32- bit units. Compared to smaller bit widths, 32-bit computers can perform large calculati ...

links and utilizing the full HyperTransport 3.1 specification's operating frequency, the theoretical transfer rate is 25.6 GB/s (3.2 GHz × 2 transfers per clock cycle × 32 bits per link) per direction, or 51.2 GB/s aggregated throughput, making it faster than most existing bus standard for PC workstations and servers as well as making it faster than most bus standards for high-performance computing and networking.

Links of various widths can be mixed together in a single system configuration as in one 16-bit

16-bit microcomputers are microcomputers that use 16-bit microprocessors.

A 16-bit register can store 216 different values. The range of integer values that can be stored in 16 bits depends on the integer representation used. With the two ...

link to another CPU and one 8-bit

In computer architecture, 8-bit integers or other data units are those that are 8 bits wide (1 octet). Also, 8-bit central processing unit (CPU) and arithmetic logic unit (ALU) architectures are those that are based on registers or data buses ...

link to a peripheral device, which allows for a wider interconnect between CPUs, and a lower bandwidth interconnect to peripheral

A peripheral or peripheral device is an auxiliary device used to put information into and get information out of a computer. The term ''peripheral device'' refers to all hardware components that are attached to a computer and are controlled by the ...

s as appropriate. It also supports link splitting, where a single 16-bit link can be divided into two 8-bit links. The technology also typically has lower latency than other solutions due to its lower overhead.

Electrically, HyperTransport is similar to low-voltage differential signaling

Low-voltage differential signaling (LVDS), also known as TIA/EIA-644, is a technical standard that specifies electrical characteristics of a differential, serial signaling standard. LVDS operates at low power and can run at very high speeds ...

(LVDS) operating at 1.2 V. HyperTransport 2.0 added post-cursor transmitter deemphasis. HyperTransport 3.0 added scrambling and receiver phase alignment as well as optional transmitter precursor deemphasis.

Packet-oriented

HyperTransport is packet-based, where each packet consists of a set of32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32- bit units. Compared to smaller bit widths, 32-bit computers can perform large calculati ...

words, regardless of the physical width of the link. The first word in a packet always contains a command field. Many packets contain a 40-bit address. An additional 32-bit control packet is prepended when 64-bit addressing is required. The data payload is sent after the control packet. Transfers are always padded to a multiple of 32 bits, regardless of their actual length.

HyperTransport packets enter the interconnect in segments known as bit times. The number of bit times required depends on the link width. HyperTransport also supports system management messaging, signaling interrupts, issuing probes to adjacent devices or processors, I/O transactions, and general data transactions. There are two kinds of write commands supported: posted and non-posted. Posted writes do not require a response from the target. This is usually used for high bandwidth devices such as uniform memory access

Uniform memory access (UMA) is a shared memory architecture used in parallel computers. All the processors in the UMA model share the physical memory uniformly. In an UMA architecture, access time to a memory location is independent of which proc ...

traffic or direct memory access

Direct memory access (DMA) is a feature of computer systems and allows certain hardware subsystems to access main system memory independently of the central processing unit (CPU).

Without DMA, when the CPU is using programmed input/output, it is ...

transfers. Non-posted writes require a response from the receiver in the form of a "target done" response. Reads also require a response, containing the read data. HyperTransport supports the PCI consumer/producer ordering model.

Power-managed

HyperTransport also facilitatespower management

Power management is a feature of some electrical appliances, especially copiers, computers, computer CPUs, computer GPUs and computer peripherals such as monitors and printers, that turns off the power or switches the system to a low-power st ...

as it is compliant with the Advanced Configuration and Power Interface

Advanced Configuration and Power Interface (ACPI) is an open standard that operating systems can use to discover and configure computer hardware components, to perform power management (e.g. putting unused hardware components to sleep), auto co ...

specification. This means that changes in processor sleep states (C states) can signal changes in device states (D states), e.g. powering off disks when the CPU goes to sleep. HyperTransport 3.0 added further capabilities to allow a centralized power management controller to implement power management policies.

Applications

Front-side bus replacement

The primary use for HyperTransport is to replace the Intel-defined front-side bus, which is different for every type of Intel processor. For instance, aPentium

Pentium is a brand used for a series of x86 architecture-compatible microprocessors produced by Intel. The original Pentium processor from which the brand took its name was first released on March 22, 1993. After that, the Pentium II and P ...

cannot be plugged into a PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common ...

bus directly, but must first go through an adapter to expand the system. The proprietary front-side bus must connect through adapters for the various standard buses, like AGP or PCI Express. These are typically included in the respective controller functions, namely the '' northbridge'' and '' southbridge''.

In contrast, HyperTransport is an open specification, published by a multi-company consortium. A single HyperTransport adapter chip will work with a wide spectrum of HyperTransport enabled microprocessors.

AMD used HyperTransport to replace the front-side bus in their Opteron

Opteron is AMD's x86 former server and workstation processor line, and was the first processor which supported the AMD64 instruction set architecture (known generically as x86-64 or AMD64). It was released on April 22, 2003, with the ''Sledg ...

, Athlon 64

The Athlon 64 is a ninth-generation, AMD64-architecture microprocessor produced by Advanced Micro Devices (AMD), released on September 23, 2003. It is the third processor to bear the name ''Athlon'', and the immediate successor to the Athlon XP. T ...

, Athlon II, Sempron 64, Turion 64, Phenom, Phenom II

Phenom II is a family of AMD's multi-core 45 nm processors using the AMD K10 microarchitecture, succeeding the original Phenom. Advanced Micro Devices released the Socket AM2+ version of Phenom II in December 2008, while Socket AM3 version ...

and FX families of microprocessors.

Multiprocessor interconnect

Another use for HyperTransport is as an interconnect forNUMA

Nuclear mitotic apparatus protein 1 is a protein that in humans is encoded by the ''NUMA1'' gene.

Interactions

Nuclear mitotic apparatus protein 1 has been shown to interact with PIM1, Band 4.1, GPSM2

G-protein-signaling modulator 2, also ca ...

multiprocessor

Multiprocessing is the use of two or more central processing units (CPUs) within a single computer system. The term also refers to the ability of a system to support more than one processor or the ability to allocate tasks between them. There ar ...

computers. AMD used HyperTransport with a proprietary cache coherency

In computer architecture, cache coherence is the uniformity of shared resource data that ends up stored in multiple local caches. When clients in a system maintain caches of a common memory resource, problems may arise with incoherent data, whi ...

extension as part of their Direct Connect Architecture in their Opteron

Opteron is AMD's x86 former server and workstation processor line, and was the first processor which supported the AMD64 instruction set architecture (known generically as x86-64 or AMD64). It was released on April 22, 2003, with the ''Sledg ...

and Athlon 64 FX ( Dual Socket Direct Connect (DSDC) Architecture) line of processors. Infinity Fabric used with the EPYC

Epyc is a brand of multi-core x86-64 microprocessors designed and sold by AMD, based on the company's Zen microarchitecture. Introduced in June 2017, they are specifically targeted for the server and embedded system markets. Epyc processors share ...

server CPUs is a superset of HyperTransport. The HORUS interconnect from Newisys

Newisys was an American technology company. At various times it sold computers for data centers (known as servers), and computer data storage products.

It operated as a subsidiary of Sanmina Corporation since 2004.

History

Newisys was founded in ...

extends this concept to larger clusters. The Aqua device from 3Leaf Systems virtualizes and interconnects CPUs, memory, and I/O.

Router or switch bus replacement

HyperTransport can also be used as a bus in routers and switches. Routers and switches have multiple network interfaces, and must forward data between these ports as fast as possible. For example, a four-port, 1000Mbit

The megabit is a multiple of the unit bit for digital information. The prefix mega (symbol M) is defined in the International System of Units (SI) as a multiplier of 106 (1 million), and therefore

:1 megabit = = = 1000 kilobits.

The megabit ...

/s Ethernet

Ethernet () is a family of wired computer networking technologies commonly used in local area networks (LAN), metropolitan area networks (MAN) and wide area networks (WAN). It was commercially introduced in 1980 and first standardized in 1 ...

router needs a maximum 8000 Mbit/s of internal bandwidth (1000 Mbit/s × 4 ports × 2 directions)—HyperTransport greatly exceeds the bandwidth this application requires. However a 4 + 1 port 10 Gb router would require 100 Gbit/s of internal bandwidth. Add to that 802.11ac 8 antennas and the WiGig 60 GHz standard (802.11ad) and HyperTransport becomes more feasible (with anywhere between 20 and 24 lanes used for the needed bandwidth).

Co-processor interconnect

The issue of latency and bandwidth between CPUs and co-processors has usually been the major stumbling block to their practical implementation. Co-processors such asFPGAs

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturinghence the term '' field-programmable''. The FPGA configuration is generally specified using a hardware de ...

have appeared that can access the HyperTransport bus and become integrated on the motherboard. Current generation FPGAs from both main manufacturers (Altera

Altera Corporation was a manufacturer of programmable logic devices (PLDs) headquartered in San Jose, California. It was founded in 1983 and acquired by Intel in 2015.

The main product lines from Altera were the flagship Stratix series, mid-ran ...

and Xilinx

Xilinx, Inc. ( ) was an American technology and semiconductor company that primarily supplied programmable logic devices. The company was known for inventing the first commercially viable field-programmable gate array (FPGA) and creating the fi ...

) directly support the HyperTransport interface, and have IP Cores available. Companies such as XtremeData, Inc. and DRC take these FPGAs (Xilinx in DRC's case) and create a module that allows FPGAs to plug directly into the Opteron socket.

AMD started an initiative named Torrenza on September 21, 2006 to further promote the usage of HyperTransport for plug-in cards and coprocessors

A coprocessor is a computer processor used to supplement the functions of the primary processor (the CPU). Operations performed by the coprocessor may be floating-point arithmetic, graphics, signal processing, string processing, cryptography or ...

. This initiative opened their "Socket F" to plug-in boards such as those from XtremeData and DRC.

Add-on card connector (HTX and HTX3)

A connector specification that allows a slot-based peripheral to have direct connection to a microprocessor using a HyperTransport interface was released by the HyperTransport Consortium. It is known as HyperTransport eXpansion (HTX). Using a reversed instance of the same mechanical connector as a 16-lane

A connector specification that allows a slot-based peripheral to have direct connection to a microprocessor using a HyperTransport interface was released by the HyperTransport Consortium. It is known as HyperTransport eXpansion (HTX). Using a reversed instance of the same mechanical connector as a 16-lane PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common ...

slot (plus an x1 connector for power pins), HTX allows development of plug-in cards that support direct access to a CPU and DMA

DMA may refer to:

Arts

* DMA (magazine), ''DMA'' (magazine), a defunct dance music magazine

* Dallas Museum of Art, an art museum in Texas, US

* Danish Music Awards, an award show held in Denmark

* BT Digital Music Awards, an annual event in the U ...

to the system RAM

Ram, ram, or RAM may refer to:

Animals

* A male sheep

* Ram cichlid, a freshwater tropical fish

People

* Ram (given name)

* Ram (surname)

* Ram (director) (Ramsubramaniam), an Indian Tamil film director

* RAM (musician) (born 1974), Dutch

* ...

. The initial card for this slot was the QLogic InfiniPath InfiniBand HCA. IBM and HP, among others, have released HTX compliant systems.

The original HTX standard is limited to 16bits and 800MHz.

In August 2008, the HyperTransport Consortium released HTX3, which extends the clock rate of HTX to 2.6 GHz (5.2 GT/s, 10.7 GTi, 5.2 real GHz data rate, 3 MT/s edit rate) and retains backwards compatibility.

Testing

The "DUT" test connector is defined to enable standardized functional test system interconnection.Implementations

* AMDAMD64

x86-64 (also known as x64, x86_64, AMD64, and Intel 64) is a 64-bit version of the x86 instruction set, first released in 1999. It introduced two new modes of operation, 64-bit mode and compatibility mode, along with a new 4-level paging m ...

and Direct Connect Architecture based CPUs

* AMD chipsets

** AMD-8000 series

** AMD 480 series

** AMD 580 series

** AMD 690 series

** AMD 700 series

** AMD 800 series

** AMD 900 series

* ATI

Ati or ATI may refer to:

* Ati people, a Negrito ethnic group in the Philippines

**Ati language (Philippines), the language spoken by this people group

** Ati-Atihan festival, an annual celebration held in the Philippines

*Ati language (China), a ...

chipsets

** ATI Radeon Xpress 200 for AMD processor

** ATI Radeon Xpress 3200 for AMD processor

* Broadcom

Broadcom Inc. is an American designer, developer, manufacturer and global supplier of a wide range of semiconductor and infrastructure software products. Broadcom's product offerings serve the data center, networking, software, broadband, wirel ...

(then ServerWorks

ServerWorks Corporation was an American fabless semiconductor company based in Santa Clara, California, that manufactured chipsets for server computers and workstations running IA-32 microprocessors. Founded as Reliance Computer Corporatio ...

) HyperTransport SystemI/O controllers

** HT-2000

** HT-2100

* Cisco

Cisco Systems, Inc., commonly known as Cisco, is an American-based multinational digital communications technology conglomerate corporation headquartered in San Jose, California. Cisco develops, manufactures, and sells networking hardware, ...

QuantumFlow Processors

* ht_tunnel from OpenCores

OpenCores is a community developing digital open-source hardware through electronic design automation (EDA), with a similar ethos as the free software movement. OpenCores hopes to eliminate redundant design work and slash development costs. A n ...

project (MPL licence)

* IBM CPC925 and CPC945 ( PowerPC 970 northbridges) chipsets

* Loongson-3 MIPS processor

* Nvidia

Nvidia CorporationOfficially written as NVIDIA and stylized in its logo as VIDIA with the lowercase "n" the same height as the uppercase "VIDIA"; formerly stylized as VIDIA with a large italicized lowercase "n" on products from the mid 1990s to ...

nForce chipsets

** nForce Professional MCPs (Media and Communication Processor)

** nForce 3 series

** nForce 4

The nForce4 is a motherboard chipset released by Nvidia in October 2004. The chipset supports AMD 64-bit processors (Socket 939, Socket AM2 and Socket 754) and Intel Pentium 4 LGA 775 processors.

Models nForce4/nForce4-4x

nForce4 is the second ...

series

** nForce 500 series

** nForce 600 series

** nForce 700 series

** nForce 900 series

* PMC-Sierra

PMC-Sierra was a global fabless semiconductor company with offices worldwide that developed and sold semiconductor devices into the storage, communications, optical networking, printing, and embedded computing marketplaces.

On January 15, 2016, ...

RM9000X2 MIPS CPU

* Power Mac G5

* Raza Thread Processors

* SiByte MIPS CPUs from Broadcom

Broadcom Inc. is an American designer, developer, manufacturer and global supplier of a wide range of semiconductor and infrastructure software products. Broadcom's product offerings serve the data center, networking, software, broadband, wirel ...

* Transmeta

Transmeta Corporation was an American fabless semiconductor company based in Santa Clara, California. It developed low power x86 compatible microprocessors based on a VLIW core and a software layer called Code Morphing Software.

Code Morphing S ...

TM8000 Efficeon CPUs

* VIA

Via or VIA may refer to the following:

Science and technology

* MOS Technology 6522, Versatile Interface Adapter

* ''Via'' (moth), a genus of moths in the family Noctuidae

* Via (electronics), a through-connection

* VIA Technologies, a Taiwa ...

chipsets K8 series

Frequency specifications

Athlon 64

The Athlon 64 is a ninth-generation, AMD64-architecture microprocessor produced by Advanced Micro Devices (AMD), released on September 23, 2003. It is the third processor to bear the name ''Athlon'', and the immediate successor to the Athlon XP. T ...

, Athlon 64 FX, Athlon 64 X2

The Athlon 64 X2 is the first native dual-core desktop central processing unit (CPU) designed by Advanced Micro Devices (AMD). It was designed from scratch as native dual-core by using an already multi-CPU enabled Athlon 64, joining it with anot ...

, Athlon X2, Athlon II, Phenom, Phenom II

Phenom II is a family of AMD's multi-core 45 nm processors using the AMD K10 microarchitecture, succeeding the original Phenom. Advanced Micro Devices released the Socket AM2+ version of Phenom II in December 2008, while Socket AM3 version ...

, Sempron, Turion series and later use one 16-bit HyperTransport link. AMD Athlon 64 FX (1207

Year 1207 ( MCCVII) was a common year starting on Monday ( full calendar) under the Julian calendar.

Events

By place

Byzantine Empire

* Spring – Siege of Attalia: Seljuk forces led by Sultan Kaykhusraw I besiege the city por ...

), Opteron

Opteron is AMD's x86 former server and workstation processor line, and was the first processor which supported the AMD64 instruction set architecture (known generically as x86-64 or AMD64). It was released on April 22, 2003, with the ''Sledg ...

use up to three 16-bit HyperTransport links. Common clock rates for these processor links are 800 MHz to 1 GHz (older single and multi socket systems on 754/939/940 links) and 1.6 GHz to 2.0 GHz (newer single socket systems on AM2+/AM3 links—most newer CPUs using 2.0GHz). While HyperTransport itself is capable of 32-bit width links, that width is not currently utilized by any AMD processors. Some chipsets though do not even utilize the 16-bit width used by the processors. Those include the Nvidia nForce3 150, nForce3 Pro 150, and the ULi

Uli may refer to:

*Uli, Iran, a village

*Uli, Anambra, a town in Nigeria

* Uli I of Mali

* Uli (design), by the Igbo people of Nigeria

* Uli figure, from New Ireland, Papua New Guinea

* Uli (food), a rice-based food

* ISO 639 code for the Ulithian ...

M1689—which use a 16-bit HyperTransport downstream link but limit the HyperTransport upstream link to 8 bits.

Name

There has been some marketing confusion between the use of HT referring to HyperTransport and the later use of HT to refer toIntel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California. It is the world's largest semiconductor chip manufacturer by revenue, and is one of the developers of the x86 ser ...

's Hyper-Threading

Hyper-threading (officially called Hyper-Threading Technology or HT Technology and abbreviated as HTT or HT) is Intel's proprietary simultaneous multithreading (SMT) implementation used to improve parallelization of computations (doing multipl ...

feature on some Pentium 4

Pentium 4 is a series of single-core CPUs for desktops, laptops and entry-level servers manufactured by Intel. The processors were shipped from November 20, 2000 until August 8, 2008. The production of Netburst processors was active from 2000 ...

-based and the newer Nehalem and Westmere-based Intel Core

Intel Core is a line of streamlined midrange consumer, workstation and enthusiast computer central processing units (CPUs) marketed by Intel Corporation. These processors displaced the existing mid- to high-end Pentium processors at the time o ...

microprocessors. Hyper-Threading is officially known as Hyper-Threading Technology (HTT) or HT Technology. Because of this potential for confusion, the HyperTransport Consortium always uses the written-out form: "HyperTransport."

Infinity Fabric

Infinity Fabric (IF) is a superset of HyperTransport announced by AMD in 2016 as an interconnect for its GPUs and CPUs. It is also usable as interchip interconnect for communication between CPUs and GPUs (for Heterogeneous System Architecture), an arrangement known as Infinity Architecture. The company said the Infinity Fabric would scale from 30GB/s to 512GB/s, and be used in theZen

Zen ( zh, t=禪, p=Chán; ja, text= 禅, translit=zen; ko, text=선, translit=Seon; vi, text=Thiền) is a school of Mahayana Buddhism that originated in China during the Tang dynasty, known as the Chan School (''Chánzong'' 禪宗), and ...

-based CPUs and Vega

Vega is the brightest star in the northern constellation of Lyra. It has the Bayer designation α Lyrae, which is Latinised to Alpha Lyrae and abbreviated Alpha Lyr or α Lyr. This star is relatively close at only from the Sun, a ...

GPUs which were subsequently released in 2017.

On Zen and Zen+

Zen ( zh, t=禪, p=Chán; ja, text= 禅, translit=zen; ko, text=선, translit=Seon; vi, text=Thiền) is a school of Mahayana Buddhism that originated in China during the Tang dynasty, known as the Chan School (''Chánzong'' 禪宗), and ...

CPUs, the "SDF" data interconnects are run at the same frequency as the DRAM memory clock (MEMCLK), a decision made to remove the latency caused by different clock speeds. As a result, using a faster RAM module makes the entire bus faster. The links are 32-bit wide, as in HT, but 8 transfers are done per cycle (128-bit packets) compared to the original 2. Electrical changes are made for higher power efficiency. On Zen 2

Zen 2 is a computer processor microarchitecture by AMD. It is the successor of AMD's Zen and Zen+ microarchitectures, and is fabricated on the 7 nanometer MOSFET node from TSMC. The microarchitecture powers the third generation of Ryzen proces ...

and Zen 3

Zen 3 is the codename for a CPU microarchitecture by AMD, released on November 5, 2020. It is the successor to Zen 2 and uses TSMC's 7 nm process for the chiplets and GlobalFoundries's 14 nm process for the I/O die on the server chips and 12 nm ...

CPUs, the IF bus is on a separate clock, either in a 1:1 or 2:1 ratio to the DRAM clock, because of Zen's early problems with high-speed DRAM affecting IF speed, and therefore system stability. The bus width has also been doubled.

See also

* Elastic interface bus *Fibre Channel

Fibre Channel (FC) is a high-speed data transfer protocol providing in-order, lossless delivery of raw block data. Fibre Channel is primarily used to connect computer data storage to servers in storage area networks (SAN) in commercial data cen ...

* Front-side bus

* Intel QuickPath Interconnect

* List of device bandwidths

This is a list of interface bit rates, is a measure of information transfer rates, or digital bandwidth capacity, at which digital interfaces in a computer or network can communicate over various kinds of buses and channels. The distinction can ...

* PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common ...

* RapidIO

* AGESA

References

External links

* * . * * {{Computer-bus Computer buses Macintosh internals Serial buses