Programmable Array Logic (PAL) is a family of programmable logic device semiconductors used to implement logic functions in digital circuits introduced by Monolithic Memories, Inc. (MMI) in March 1978. Introductory advertisement on PAL (Programmable Array Logic). MMI obtained a registered trademark on the term PAL for use in "Programmable Semiconductor Logic Circuits". The trademark is currently held by Lattice Semiconductor.Monolithic Memories, Inc (MMI) filed for a work mark on the term "PAL" for use in "Programmable Semiconductor Logic Circuits" on April 13, 1978. A registered trademark was granted on April 29, 1980, registration number 1134025. MMI's first use of the term PAL in commerce was on February 21, 1978. The trademark is currently held by Lattice Semiconductor Corporation of Hillsboro, Oregon. Source: United States Patent and Trademark Office online database.

PAL devices consisted of a small PROM (programmable read-only memory) core and additional output logic used to implement particular desired logic functions with few components.

Using specialized machines, PAL devices were "field-programmable". PALs were available in several variants:

* "

Programmable Array Logic (PAL) is a family of programmable logic device semiconductors used to implement logic functions in digital circuits introduced by Monolithic Memories, Inc. (MMI) in March 1978. Introductory advertisement on PAL (Programmable Array Logic). MMI obtained a registered trademark on the term PAL for use in "Programmable Semiconductor Logic Circuits". The trademark is currently held by Lattice Semiconductor.Monolithic Memories, Inc (MMI) filed for a work mark on the term "PAL" for use in "Programmable Semiconductor Logic Circuits" on April 13, 1978. A registered trademark was granted on April 29, 1980, registration number 1134025. MMI's first use of the term PAL in commerce was on February 21, 1978. The trademark is currently held by Lattice Semiconductor Corporation of Hillsboro, Oregon. Source: United States Patent and Trademark Office online database.

PAL devices consisted of a small PROM (programmable read-only memory) core and additional output logic used to implement particular desired logic functions with few components.

Using specialized machines, PAL devices were "field-programmable". PALs were available in several variants:

* "One-time programmable

A programmable read-only memory (PROM) is a form of digital memory where the contents can be changed once after manufacture of the device. The data is then permanent and cannot be changed. It is one type of read-only memory (ROM). PROMs are used ...

" (OTP) devices could not be updated and reused after initial programming (MMI also offered a similar family called HAL, or "hard array logic", which were like PAL devices except that they were mask-programmed at the factory.).

* UV erasable versions (e.g.: PALCxxxxx e.g.: PALC22V10) had a quartz window over the chip die and could be erased for re-use with an ultraviolet light source just like an EPROM.

* Later versions (PALCExxx e.g.: PALCE22V10) were flash erasable devices.

In most applications, electrically-erasable GALs are now deployed as pin-compatible direct replacements for one-time programmable PALs.

History

Before PALs were introduced, designers of digital logic circuits would use small-scale integration (SSI) components, such as those in the 7400 series TTL ( transistor-transistor logic) family; the 7400 family included a variety of logic building blocks, such as gates ( NOT, NAND, NOR, AND, OR),multiplexers

In electronics, a multiplexer (or mux; spelled sometimes as multiplexor), also known as a data selector, is a device that selects between several analog or digital input signals and forwards the selected input to a single output line. The sele ...

(MUXes) and demultiplexers (DEMUXes), flip flops

Flip-flops are a type of light sandal, typically worn as a form of casual footwear. They consist of a flat sole held loosely on the foot by a Y-shaped strap known as a toe thong that passes between the first and second toes and around both side ...

(D-type, JK, etc.) and others. One PAL device would typically replace dozens of such "discrete" logic packages, so the SSI business declined as the PAL business took off. PALs were used advantageously in many products, such as minicomputers, as documented in Tracy Kidder's best-selling book '' The Soul of a New Machine''.

PALs were not the first commercial programmable logic devices; Signetics had been selling its field programmable logic array

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturinghence the term '' field-programmable''. The FPGA configuration is generally specified using a hardware de ...

(FPLA) since 1975. These devices were completely unfamiliar to most circuit designers and were perceived to be too difficult to use. The FPLA had a relatively slow maximum operating speed (due to having both programmable-AND and programmable-OR arrays), was expensive, and had a poor reputation for testability. Another factor limiting the acceptance of the FPLA was the large package, a 600- mil (0.6", or 15.24 mm) wide 28-pin dual in-line package

In microelectronics, a dual in-line package (DIP or DIL), is an electronic component package with a rectangular housing and two parallel rows of electrical connecting pins. The package may be through-hole mounted to a printed circuit board (P ...

(DIP).

The project to create the PAL device was managed by John Birkner and the actual PAL circuit was designed by H. T. Chua. In a previous job (at mini-computer manufacturer Computer Automation), Birkner had developed a 16-bit processor using 80 standard logic devices. His experience with standard logic led him to believe that user-programmable devices would be more attractive if the devices were designed to replace standard logic. This meant that the package sizes had to be more typical of the existing devices, and the speeds had to be improved. MMI intended PALs to be a relatively low cost (sub $3) part. However, the company initially had severe manufacturing yield problems and had to sell the devices for over $50. This threatened the viability of the PAL as a commercial product, and MMI was forced to license the product line to National Semiconductor. PALs were later " second sourced" by Texas Instruments and Advanced Micro Devices.

Process technologies

Early PALs were 20-pin DIP components fabricated in silicon using bipolar transistor technology with one-time programmable (OTP) titanium-tungsten programming fuses. "These IMPACT circuits combine the latest Advanced Low-Power Schottky technology with proven titanium-tungsten fuses to provide reliable, high-performance substitutes for conventional TTL logic." TI was a second source vendor for the MMI PALS. Later devices were manufactured byCypress

Cypress is a common name for various coniferous trees or shrubs of northern temperate regions that belong to the family Cupressaceae. The word ''cypress'' is derived from Old French ''cipres'', which was imported from Latin ''cypressus'', the ...

, Lattice Semiconductor and Advanced Micro Devices using CMOS

Complementary metal–oxide–semiconductor (CMOS, pronounced "sea-moss", ) is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSFE ...

technology.

The original 20 and 24-pin PALs were denoted by MMI as medium-scale integration (MSI) devices.

PAL architecture

Programmable logic plane

The programmable logic plane is aprogrammable read-only memory

A programmable read-only memory (PROM) is a form of digital memory where the contents can be changed once after manufacture of the device. The data is then permanent and cannot be changed. It is one type of read-only memory (ROM). PROMs are used ...

(PROM) array that allows the signals present on the device pins, or the logical complements of those signals, to be routed to output logic macrocells.

PAL devices have arrays of transistor cells arranged in a "fixed-OR, programmable-AND" plane used to implement " sum-of-products" binary logic equations for each of the outputs in terms of the inputs and either synchronous or asynchronous feedback from the outputs.

Output logic

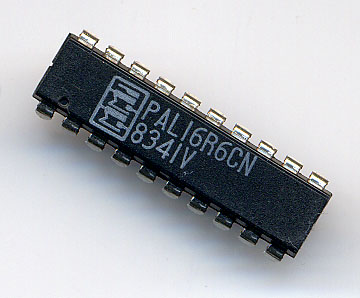

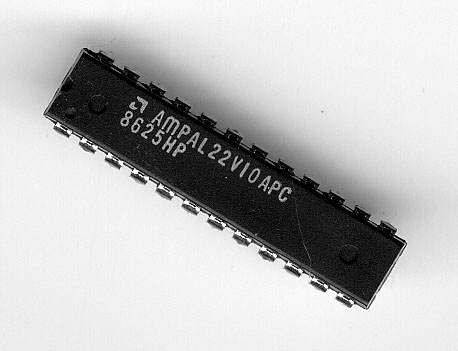

The early 20-pin PALs had 10 inputs and 8 outputs. The outputs were active low and could be registered or combinational. Members of the PAL family were available with various output structures called " output logic macrocells" or OLMCs. Prior to the introduction of the "V" (for "variable") series, the types of OLMCs available in each PAL were fixed at the time of manufacture. (The PAL16L8 had 8 combinational outputs, and the PAL16R8 had 8 registered outputs. The PAL16R6 had 6 registered and 2 combinational, while the PAL16R4 had 4 of each.) Each output could have up to 8 product terms (effectively AND gates); however, the combinational outputs used one of the terms to control a bidirectional output buffer. There were other combinations that had fewer outputs with more product terms per output and were available with active high outputs ("H" series). The "X" series of devices had an XOR gate before the register. There were also similar 24-pin versions of these PALs. This fixed output structure often frustrated designers attempting to optimize the utility of PAL devices because output structures of different types were often required by their applications. (For example, one could not get 5 registered outputs with 3 active high combinational outputs.) So, in June 1983 AMD introduced the 22V10, a 24 pin device with 10 output logic macrocells. Note: This is the data sheet published by AMD when the AmPAL 22V10 was introduced. Each macrocell could be configured by the user to be combinational or registered, active high or active low. The number of product terms allocated to an output varied from 8 to 16. This one device could replace all of the 24 pin fixed function PAL devices. Members of the PAL "V" ("variable") series included the PAL16V8, PAL20V8 and PAL22V10.Programming PALs

PALs were programmed electrically using binary patterns (as JEDEC ASCII/hexadecimal

In mathematics and computing, the hexadecimal (also base-16 or simply hex) numeral system is a positional numeral system that represents numbers using a radix (base) of 16. Unlike the decimal system representing numbers using 10 symbols, hexa ...

files) and a special electronic programming system available from either the manufacturer or a third-party, such as DATA I/O

Data I/O is a provider of manual and automated data programming and security provisioning systems for flash memory, microcontroller and logic devices, founded in 1972. The company develops products used for the design and manufacturing of system ...

. In addition to single-unit device programmers, device feeders and gang programmers were often used when more than just a few PALs needed to be programmed. (For large volumes, electrical programming costs could be eliminated by having the manufacturer fabricate a custom metal mask used to program the customers' patterns at the time of manufacture; MMI used the term " hard array logic" (HAL) to refer to devices programmed in this way.)

Programming languages (by chronological order of appearance)

Though some engineers programmed PAL devices by manually editing files containing the binary fuse pattern data, most opted to design their logic using a hardware description language (HDL) such as Data I/O's ABEL, Logical Devices' CUPL, or MMI's PALASM. These were

Though some engineers programmed PAL devices by manually editing files containing the binary fuse pattern data, most opted to design their logic using a hardware description language (HDL) such as Data I/O's ABEL, Logical Devices' CUPL, or MMI's PALASM. These were computer-assisted design

Computer-aided design (CAD) is the use of computers (or ) to aid in the creation, modification, analysis, or optimization of a design. This software is used to increase the productivity of the designer, improve the quality of design, improve co ...

( CAD) (now referred to as "electronic design automation

Electronic design automation (EDA), also referred to as electronic computer-aided design (ECAD), is a category of software tools for designing Electronics, electronic systems such as integrated circuits and printed circuit boards. The tools wo ...

") programs which translated (or "compiled") the designers' logic equations into binary fuse map files used to program (and often test) each device.

PALASM

The PALASM (from "PAL assembler") language was developed by John Birkner in the early 1980s and the PALASM compiler was written by MMI in FORTRAN IV on an IBM 370/168. MMI made the source code available to users at no cost. By 1983, MMI customers ran versions on the DECPDP-11

The PDP-11 is a series of 16-bit minicomputers sold by Digital Equipment Corporation (DEC) from 1970 into the 1990s, one of a set of products in the Programmed Data Processor (PDP) series. In total, around 600,000 PDP-11s of all models were sold, ...

, Data General NOVA, Hewlett-Packard

The Hewlett-Packard Company, commonly shortened to Hewlett-Packard ( ) or HP, was an American multinational information technology company headquartered in Palo Alto, California. HP developed and provided a wide variety of hardware components ...

HP 2100, MDS800 and others.

It was used to express boolean equations for the output pins in a text file which was then converted to the 'fuse map' file for the programming system using a vendor-supplied program; later the option of translation from schematics became common, and later still, 'fuse maps' could be 'synthesized' from an HDL (hardware description language) such as Verilog.

CUPL

Assisted Technology released CUPL (Compiler for Universal Programmable Logic) in September 1983. The software was always referred to as CUPL and never the expanded acronym. It was the first commercial design tool that supported multiple PLD families. The initial release was for the IBM PC and MS-DOS, but it was written in theC programming language

''The C Programming Language'' (sometimes termed ''K&R'', after its authors' initials) is a computer programming book written by Brian Kernighan and Dennis Ritchie, the latter of whom originally designed and implemented the language, as well as ...

so it could be ported to additional platforms. An early 1983 pre-release datasheet for CUPL. Assisted Technology was acquired by Personal CAD Systems (P-CAD) in July 1985. In 1986, PCAD's schematic capture package could be used as a front end for CUPL. CUPL was later acquired by Logical Devices and is now owned by Altium.US Patent and Trademark Office. "CUPL" Computer software, namely, software used to develop and compile designs for programmable logic devices, and related user manuals distributed therewith. First used in 1983, status Active. Serial Number 76357007. Registration Number 2909461. Owner: Altium Limited, Australia 3 Minna Close, Belrose NSW2085, Australia. CUPL is currently available as an integrated development package for Microsoft Windows.

Atmel releases for freWinCUPL

(their own design software for all Atmel SPLDs and CPLDs). Atmel was acquired by Microchip.

ABEL

Data I/O Corporation released ABEL in April, 1984. The development team was Michael Holley, Mike Mraz, Gerrit Barrere, Walter Bright, Bjorn Freeman-Benson, Kyu Lee, David Pellerin, Mary Bailey, Daniel Burrier and Charles Olivier. Data I/O spun off the ABEL product line into an EDA company called Synario Design Systems and then sold Synario to MINC Inc in 1997. MINC was focused on developing FPGA development tools. The company closed its doors in 1998 and Xilinx acquired some of MINC's assets including the ABEL language and tool set. ABEL then became part of the Xilinx Webpack tool suite. Now Xilinx owns ABEL.Device programmers

Popular device programmers included Data I/O Corporation's Model 60A Logic Programmer and Model 2900. One of the first PAL Programmers was the Structured Design SD20/24. They had the PALASM software built-in and only required a CRT terminal to enter the equations and view the fuse plots. After fusing, the outputs of the PAL could be verified if test vectors were entered in the source file.Successors

After MMI succeeded with the 20-pin PAL parts introduced circa 1978, AMD introduced the 24-pin 22V10 PAL with additional features. After buying out MMI (circa 1987), AMD spun off a consolidated operation as Vantis, and that business was acquired by Lattice Semiconductor in 1999. Altera introduced the EP300 (first CMOS PAL) in 1983 and later moved into the FPGA business. Lattice Semiconductor introduced the generic array logic ( GAL) family in 1985, with functional equivalents of the "V" series PALs that used reprogrammable logic planes based onEEPROM

EEPROM (also called E2PROM) stands for electrically erasable programmable read-only memory and is a type of non-volatile memory used in computers, usually integrated in microcontrollers such as smart cards and remote keyless systems, or as a ...

(electrically eraseable programmable read-only memory) technology. National Semiconductor was a second source for GAL parts.

AMD introduced a similar family called PALCE. In general one GAL part is able to function as any of the similar family PAL devices. For example, the 16V8 GAL is able to replace the 16L8, 16H8, 16H6, 16H4, 16H2 and 16R8 PALs (and many others besides).

ICT (International CMOS Technology) introduced the PEEL 18CV8 in 1986. The 20-pin CMOS EEPROM part could be used in place of any of the registered-output bipolar PALs and used much less power.

Larger-scale programmable logic devices were introduced by

AMD introduced a similar family called PALCE. In general one GAL part is able to function as any of the similar family PAL devices. For example, the 16V8 GAL is able to replace the 16L8, 16H8, 16H6, 16H4, 16H2 and 16R8 PALs (and many others besides).

ICT (International CMOS Technology) introduced the PEEL 18CV8 in 1986. The 20-pin CMOS EEPROM part could be used in place of any of the registered-output bipolar PALs and used much less power.

Larger-scale programmable logic devices were introduced by Atmel

Atmel Corporation was a creator and manufacturer of semiconductors before being subsumed by Microchip Technology in 2016. Atmel was founded in 1984. The company focused on embedded systems built around microcontrollers. Its products included micr ...

, Lattice Semiconductor, and others. These devices extended the PAL architecture by including multiple logic planes and/or burying logic macrocells within the logic plane(s). The term '' complex programmable logic device'' (CPLD) was introduced to differentiate these devices from their PAL and GAL predecessors, which were then sometimes referred to as ''simple programmable logic devices'' (SPLDs).

Another large programmable logic device is the field-programmable gate array

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturinghence the term '' field-programmable''. The FPGA configuration is generally specified using a hardware d ...

(FPGA). These are devices currently made by Intel (who acquired Altera) and Xilinx and other semiconductor manufacturers.

See also

* Combinational logic Other types of programmable logic devices: *Field-programmable gate array

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturinghence the term '' field-programmable''. The FPGA configuration is generally specified using a hardware d ...

(FPGA)

* Programmable logic array (PLA)

* Programmable logic device (PLD)

** Complex programmable logic device (CPLD)

** Erasable programmable logic device (EPLD)

* Field programmable logic array

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturinghence the term '' field-programmable''. The FPGA configuration is generally specified using a hardware de ...

( Signetics FPLA)

Current and former makers of programmable logic devices:

* Actel

Actel Corporation (formerly NASDAQ:ACTL) was an American manufacturer of nonvolatile, low-power field-programmable gate arrays (FPGAs), mixed-signal FPGAs, and programmable logic solutions. It was headquartered in Mountain View, California, with ...

* Advanced Micro Devices (PAL, PALCE)

* Altera (Flex, Max)

* Atmel

Atmel Corporation was a creator and manufacturer of semiconductors before being subsumed by Microchip Technology in 2016. Atmel was founded in 1984. The company focused on embedded systems built around microcontrollers. Its products included micr ...

* Cypress Semiconductor

* Intel

* Lattice Semiconductor (GAL)

* National Semiconductor (GAL)

* QuickLogic Corp.

* Signetics (FPLA)

* Texas Instruments

* Xilinx

Current and former makers of PAL device programmers:

* Data I/O Corporation

References

Further reading

;Books * ''Programmable Logic Designer's Guide''; Roger Alford; Sams Publishing; 1989; . * ''PAL Programmable Logic Handbook''; 4ed; Monolithic Memories; 1985./small> ;Databooks * ''Bipolar LSI 1984 Databook''; 5ed; Monolithic Memories; 1984.

/small> ;Specifications * ''Standard Data Transfer Format Between Data Preparation System and Programmable Logic Device Programmer''; JEDEC Standard JESD3-C; JEDEC; June 1994. {{Authority control Electronic design automation Gate arrays