Fan-out Wafer-level Packaging on:

[Wikipedia]

[Google]

[Amazon]

Fan-out wafer-level packaging (also known as wafer-level fan-out packaging, fan-out WLP, FOWL packaging, FO-WLP, FOWLP, etc.) is an

Fan-out wafer-level packaging (also known as wafer-level fan-out packaging, fan-out WLP, FOWL packaging, FO-WLP, FOWLP, etc.) is an  In contrast to standard WLP flows, in fan-out WLP the wafer is diced first. But then the dies are very precisely re-positioned on a carrier wafer or panel, with space for

In contrast to standard WLP flows, in fan-out WLP the wafer is diced first. But then the dies are very precisely re-positioned on a carrier wafer or panel, with space for

Fan-out wafer-level packaging (also known as wafer-level fan-out packaging, fan-out WLP, FOWL packaging, FO-WLP, FOWLP, etc.) is an

Fan-out wafer-level packaging (also known as wafer-level fan-out packaging, fan-out WLP, FOWL packaging, FO-WLP, FOWLP, etc.) is an integrated circuit packaging

Integrated circuit packaging is the final stage of fabrication (semiconductor), semiconductor device fabrication, in which the die (integrated circuit), die is encapsulated in a supporting case that prevents physical damage and corrosion. The ...

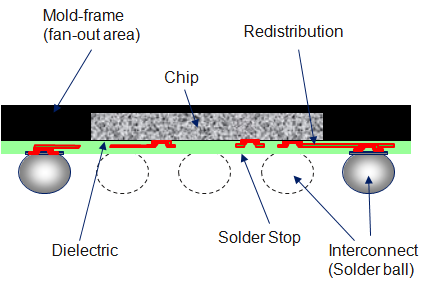

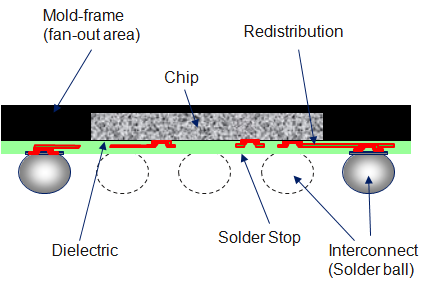

technology, and an enhancement of standard wafer-level packaging (WLP) solutions. Fan-out packaging is seen as a low cost advanced packaging alternative to packages that use silicon interposers, such as those seen in 2.5D and 3D packages.

In conventional technologies, a wafer

A wafer is a crisp, often sweet, very thin, flat, light biscuit, often used to decorate ice cream, and also used as a garnish on some sweet dishes. They frequently have a waffle surface pattern but may also be patterned with insignia of the foo ...

is diced

Dicing is a culinary knife cut in which the food item is cut into small blocks or dice. This may be done for aesthetic reasons or to create uniformly sized pieces to ensure even cooking. Dicing allows for distribution of flavour and texture thr ...

first, and then individual dies are packaged; package size is usually considerably larger than the die size. By contrast, in standard WLP flows integrated circuit

An integrated circuit (IC), also known as a microchip or simply chip, is a set of electronic circuits, consisting of various electronic components (such as transistors, resistors, and capacitors) and their interconnections. These components a ...

s are packaged while still part of the wafer, and the wafer (with outer layers of packaging already attached) is diced afterwards; the resulting package is practically of the same size as the die itself. However, the advantage of having a small package comes with a downside of limiting the number of external contacts that can be accommodated in the limited package footprint; this may become a significant limitation when complex semiconductor devices requiring a large number of contacts are considered.

Fan-out WLP was developed to relax that limitation. It provides a smaller package footprint along with improved thermal and electrical performance compared to conventional packages, and allows having higher number of contacts without increasing the die size.

In contrast to standard WLP flows, in fan-out WLP the wafer is diced first. But then the dies are very precisely re-positioned on a carrier wafer or panel, with space for

In contrast to standard WLP flows, in fan-out WLP the wafer is diced first. But then the dies are very precisely re-positioned on a carrier wafer or panel, with space for fan-out

In digital electronics, the fan-out is the number of gate inputs driven by the output of another single logic gate.

In most designs, logic gates are connected to form more complex circuits. While no logic gate input can be fed by more than one ...

kept around each die. The carrier is then reconstituted by molding, followed by making a redistribution layer

A redistribution layer (RDL) is an extra metal layer on an integrated circuit that makes its Input/output, I/O pads available in other locations of the chip, for better access to the pads where necessary.

When an integrated circuit is manufactured ...

atop the entire molded area (both atop the chip and atop the adjacent fan-out area), and then forming solder balls on top and dicing the wafer. This is known as a chip-first flow. Panel level packaging uses a large panel instead of a wafer to carry out the packaging process. High end fan-out packages are those with lines and spaces narrower than 8 microns. Fan-out packages can also have several dies, and passive components. The first fan-out packages were developed by Infineon

Infineon Semiconductor solutions is the largest microcontroller manufacturer in the world, as well as Germany's largest semiconductor manufacturer. It is also the leading automotive semiconductor manufacturer globally. Infineon had roughly 58,0 ...

in the mid-2000s for use in mobile phone chips.

See also

*List of electronic component packaging types

Integrated circuits and certain other electronic components are put into protective packages to allow easy handling and assembly onto printed circuit boards and to protect the devices from damage. A very large number of package types exist. So ...

References

External links

* * * {{cite web , url=http://www.knowmade.com/wp-content/uploads/2016/11/FOWLP_Patent_Landscape_Analysis_2016_SAMPLE.pdf , title=Fan-Out Wafer Level Packaging. Patent Landscape Analysis , date=November 2016 , df=mdy-all , publisher=Know Made Patent & Technology Intelligence , format=PDF , archive-url=https://web.archive.org/web/20180924063711/http://www.knowmade.com/wp-content/uploads/2016/11/FOWLP_Patent_Landscape_Analysis_2016_SAMPLE.pdf , archive-date=2018-09-24 , url-status=live , access-date=2018-09-24 Electronics manufacturing Semiconductor technology