|

Memory Controller

A memory controller, also known as memory chip controller (MCC) or a memory controller unit (MCU), is a digital circuit that manages the flow of data going to and from a computer's main memory. When a memory controller is integrated into another chip, such as an integral part of a microprocessor, it is usually called an integrated memory controller (IMC). Memory controllers contain the logic necessary to read and write to dynamic random-access memory (DRAM), and to provide the critical memory refresh and other functions. Reading and writing to DRAM is performed by selecting the row and column data addresses of the DRAM as the inputs to the multiplexer circuit, where the demultiplexer on the DRAM uses the converted inputs to select the correct memory location and return the data, which is then passed back through a multiplexer to consolidate the data in order to reduce the required bus width for the operation. Memory controllers' bus widths range from 8-bit in earlier systems ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Intel 82PM45 Memory Controller Hub - MCH AC82PM45-SLB97 -3718

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California, and Delaware General Corporation Law, incorporated in Delaware. Intel designs, manufactures, and sells computer components such as central processing units (CPUs) and related products for business and consumer markets. It is one of the world's List of largest semiconductor chip manufacturers, largest semiconductor chip manufacturers by revenue, and ranked in the Fortune 500, ''Fortune'' 500 list of the List of largest companies in the United States by revenue, largest United States corporations by revenue for nearly a decade, from 2007 to 2016 Fiscal year, fiscal years, until it was removed from the ranking in 2018. In 2020, it was reinstated and ranked 45th, being the List of Fortune 500 computer software and information companies, 7th-largest technology company in the ranking. It was one of the first companies listed on Nasdaq. Intel supplies List of I ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

PowerPC

PowerPC (with the backronym Performance Optimization With Enhanced RISC – Performance Computing, sometimes abbreviated as PPC) is a reduced instruction set computer (RISC) instruction set architecture (ISA) created by the 1991 Apple Inc., Apple–IBM–Motorola alliance, known as AIM alliance, AIM. PowerPC, as an evolving instruction set, has been named Power ISA since 2006, while the old name lives on as a trademark for some implementations of Power Architecture–based processors. Originally intended for personal computers, the architecture is well known for being used by Apple's desktop and laptop lines from 1994 until 2006, and in several videogame consoles including Microsoft's Xbox 360, Sony's PlayStation 3, and Nintendo's GameCube, Wii, and Wii U. PowerPC was also used for the Curiosity (rover), Curiosity and Perseverance (rover), Perseverance rovers on Mars and a variety of satellites. It has since become a niche architecture for personal computers, particularly with A ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Athlon 64

The Athlon 64 is a ninth-generation, AMD64-architecture microprocessor produced by Advanced Micro Devices (AMD), released on September 23, 2003. It is the third processor to bear the name ''Athlon'', and the immediate successor to the Athlon XP. The Athlon 64 was the second processor to implement the AMD64 architecture (after the Opteron) and the first 64-bit processor targeted at the average consumer. Variants of the Athlon 64 have been produced for Socket 754, Socket 939, Socket 940, and Socket AM2. It was AMD's primary consumer CPU, and primarily competed with Intel's Pentium 4, especially the ''Prescott'' and ''Cedar Mill'' core revisions. The Athlon 64 is AMD's first K8, eighth-generation processor core for desktop and mobile computers. Despite being natively 64-bit, the AMD64 architecture is backward-compatible with 32-bit x86 instructions. The Athlon 64 line was succeeded by the dual-core Athlon 64 X2 and Athlon X2 lines. Background The Athlon 64 was originally ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

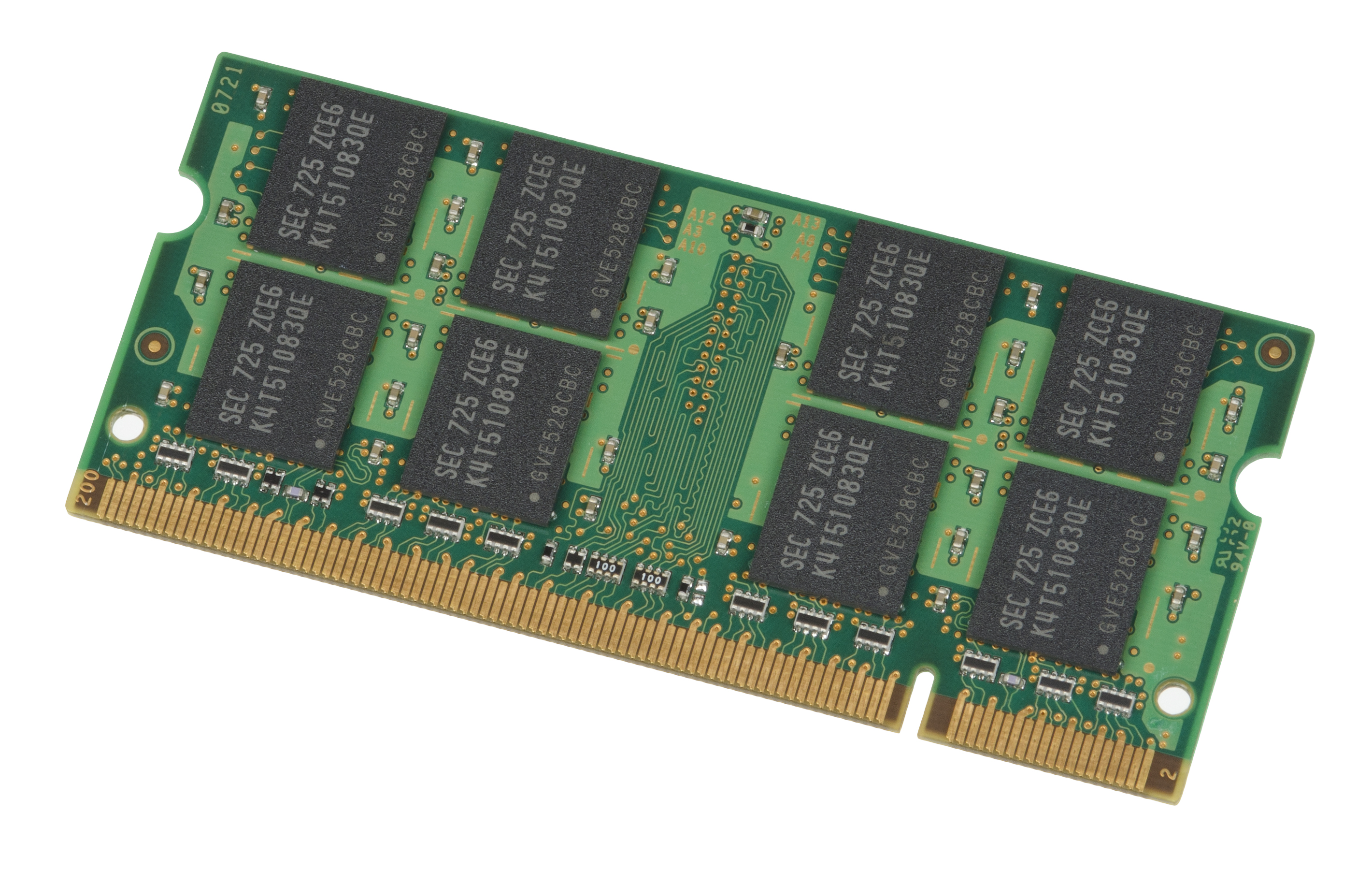

DDR2 SDRAM

Double Data Rate 2 Synchronous Dynamic Random-Access Memory (DDR2 SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) interface. It is a JEDEC standard (JESD79-2); first published in September 2003. DDR2 succeeded the original DDR SDRAM specification, and was itself succeeded by DDR3 SDRAM in 2007. DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR. In addition to double pumping the data bus as in DDR SDRAM (transferring data on the rising and falling edges of the bus clock signal), DDR2 allows higher bus speed and requires lower power by running the internal clock at half the speed of the data bus. The two factors combine to produce a total of four data transfers per internal clock cycle. Since the DDR2 internal clock runs at half the DDR external clock rate, DDR2 memory operating at the same external data bus clock rate as DDR results in DDR2 being able to provide the same bandwidth but with better la ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Memory Latency

''Memory latency'' is the time (the latency) between initiating a request for a byte or word in memory until it is retrieved by a processor. If the data are not in the processor's cache, it takes longer to obtain them, as the processor will have to communicate with the external memory cells. Latency is therefore a fundamental measure of the speed of memory: the less the latency, the faster the reading operation. Latency should not be confused with memory bandwidth, which measures the throughput of memory. Latency can be expressed in clock cycles or in time measured in nanoseconds. Over time, memory latencies expressed in clock cycles have been fairly stable, but they have improved in time.Crucial Technology, "Speed ''vs.'' Latency: Why CAS latency isn't an accurate measure of memory performance/ref> See also * Burst mode (computing) * CAS latency * Multi-channel memory architecture * Interleaved memory In computing, interleaved memory is a design which compensates for the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

UltraSPARC T1

The UltraSPARC T1 (codenamed "Niagara") is a Multithreading (computer architecture), multithreading, Multi-core processor, multicore central processing unit, CPU released by Sun Microsystems in 2005. Designed to lower the energy consumption of server (computing)#Hardware, server computers, the CPU typically uses 72 watt, W of power at 1.4 GHz. The T1 is a new-from-the-ground-up SPARC microprocessor implementation that conforms to the UltraSPARC Architecture 2005 specification and executes the full SPARC V9 instruction set. Sun has produced two previous multicore processors (UltraSPARC IV and IV+), but UltraSPARC T1 was its first microprocessor that is both multicore ''and'' multithreaded. Security was built-in from the very first release on silicon, with hardware cryptographic units in the T1, unlike general purpose processor from competing vendors of the time. The processor is available with four, six or eight CPU cores, each core able to handle four thread (computing), thr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Sun Microsystems

Sun Microsystems, Inc., often known as Sun for short, was an American technology company that existed from 1982 to 2010 which developed and sold computers, computer components, software, and information technology services. Sun contributed significantly to the evolution of several key computing technologies, among them Unix, Reduced instruction set computer, RISC processors, thin client computing, and virtualization, virtualized computing. At its height, the Sun headquarters were in Santa Clara, California (part of Silicon Valley), on the former west campus of the Agnews Developmental Center. Sun products included computer servers and workstations built on its own Reduced instruction set computer, RISC-based SPARC processor architecture, as well as on x86-based AMD Opteron and Intel Xeon processors. Sun also developed its own computer storage, storage systems and a suite of software products, including the Unix-based SunOS and later Solaris operating system, Solaris operating s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

POWER5

The POWER5 is a microprocessor developed and fabricated by IBM. It is an improved version of the POWER4. The principal improvements are support for simultaneous multithreading (SMT) and an on-die memory controller. The POWER5 is a dual-core microprocessor, with each core supporting one physical Thread (computing), thread and two logical threads, for a total of two physical threads and four logical threads. History Technical details of the microprocessor were first presented at the 2003 Hot Chips (symposium), Hot Chips conference. A more complete description was given at Microprocessor Forum 2003 on 14 October 2003. The POWER5 was not sold openly and was used exclusively by IBM and their partners. Systems using the microprocessor were introduced in 2004. The POWER5 competed in the high-end enterprise server market, mostly against the Intel Itanium 2 and to a lesser extent, the Sun Microsystems UltraSPARC IV and the Fujitsu SPARC64 V. It was superseded in 2005 by an improve ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Fermi (microarchitecture)

Fermi is the codename for a graphics processing unit (GPU) microarchitecture developed by Nvidia, first released to retail in April 2010, as the successor to the Tesla microarchitecture. It was the primary microarchitecture used in the GeForce 400 series and 500 series. All desktop Fermi GPUs were manufactured in 40nm, mobile Fermi GPUs in 40nm and 28nm. Fermi is the oldest microarchitecture from Nvidia that receives support for Microsoft's rendering API Direct3D 12 feature_level 11. Fermi was followed by Kepler, and used alongside Kepler in the GeForce 600 series, GeForce 700 series, and GeForce 800 series, in the latter two only in mobile GPUs. In the workstation market, Fermi found use in the Quadro x000 series, Quadro NVS models, and in Nvidia Tesla computing modules. The architecture is named after Enrico Fermi, an Italian physicist. Overview Fermi Graphic Processing Units ( GPUs) feature 3.0 billion transistors and a schematic is sketched in Fig. 1. *St ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

NVIDIA

Nvidia Corporation ( ) is an American multinational corporation and technology company headquartered in Santa Clara, California, and incorporated in Delaware. Founded in 1993 by Jensen Huang (president and CEO), Chris Malachowsky, and Curtis Priem, it designs and supplies graphics processing units (GPUs), application programming interfaces (APIs) for data science and high-performance computing, and system on a chip units (SoCs) for mobile computing and the automotive market. Nvidia is also a leading supplier of artificial intelligence (AI) hardware and software. Nvidia outsources the manufacturing of the hardware it designs. Nvidia's professional line of GPUs are used for edge-to-cloud computing and in supercomputers and workstations for applications in fields such as architecture, engineering and construction, media and entertainment, automotive, scientific research, and manufacturing design. Its GeForce line of GPUs are aimed at the consumer market and are used in ap ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Nehalem (microarchitecture)

Nehalem is the codename for Intel's 45 nm microarchitecture released in November 2008. It was used in the first generation of the Intel Core i5 and i7 processors, and succeeds the older Core microarchitecture used on Core 2 processors. The term "Nehalem" comes from the Nehalem River. Nehalem is built on the 45 nm process, is able to run at higher clock speeds without sacrificing efficiency, and is more energy-efficient than Penryn microprocessors. Hyper-threading is reintroduced, along with a reduction in L2 cache size, as well as an enlarged L3 cache that is shared among all cores. Nehalem is an architecture that differs radically from NetBurst, while retaining some of the latter's minor features. Nehalem later received a die-shrink to 32 nm with Westmere, and was fully succeeded by "second-generation" Sandy Bridge in January 2011. Technology * Cache line block on L2/L3 cache was reduced from 128 bytes in NetBurst & Merom/Penryn to 64 bytes per line in this gene ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

AMD K8

The AMD K8 Hammer, also code-named SledgeHammer, is a computer processor microarchitecture designed by AMD as the successor to the AMD K7 Athlon microarchitecture. The K8 was the first implementation of the AMD64 64-bit extension to the x86 instruction set architecture. Features Processors Processors based on the K8 core include: * Athlon 64 - first 64-bit consumer desktop * Athlon 64 X2 - first dual-core ('X2') desktop ** Athlon X2 - later model dual-core desktop with '64' omitted * Athlon 64 FX - enthusiast desktop (multipliers unlocked) * Sempron - low-end, low-cost desktop * Opteron - server market * Turion 64 - mobile computing market * Turion 64 X2 - dual-core mobile processor The K8 core is very similar to the K7. The most radical change is the integration of the AMD64 instructions and an on-chip memory controller. The memory controller drastically reduces memory latency and is largely responsible for most of the performance gains from K7 to K8. Nomenclat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |