|

EPYC

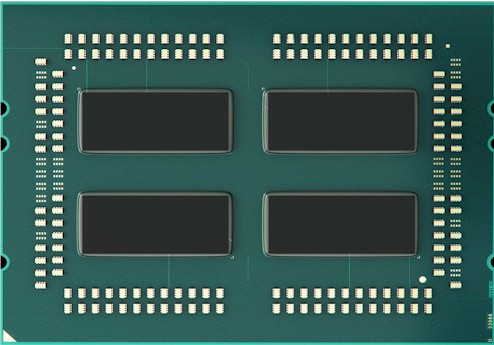

Epyc (stylized as EPYC) is a brand of multi-core x86-64 microprocessors designed and sold by AMD, based on the company's Zen microarchitecture. Introduced in June 2017, they are specifically targeted for the server and embedded system markets. Epyc processors share the same microarchitecture as their regular desktop-grade counterparts, but have enterprise-grade features such as higher core counts, more PCI Express lanes, support for larger amounts of RAM, and larger cache memory. They also support multi-chip and dual-socket system configurations by using the Infinity Fabric interconnect. History *In March 2017, AMD announced plans to re-enter the server market with a platform based on the Zen microarchitecture, codenamed Naples, and officially revealed it under the brand name Epyc in May. That June AMD officially launched Epyc 7001 series processors, offering up to 32 cores per socket, and enabling performance that allowed Epyc to be competitive with the competing Inte ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Zen (first Generation)

Zen is the first iteration in the Zen (microarchitecture), Zen family of computer processor microarchitectures from AMD. It was first used with their Ryzen series of CPUs in February 2017. The first Zen-based preview system was demonstrated at Electronic Entertainment Expo 2016, E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs, codenamed "Summit Ridge", reached the market in early March 2017, Zen-derived Epyc server processors launched in June 2017 and Zen-based AMD Accelerated Processing Unit, APUs arrived in November 2017. Zen is a clean sheet design that differs from AMD's previous long-standing Bulldozer (microarchitecture), Bulldozer architecture. Zen-based processors use a 14 nanometer, 14 nm FinFET process, are reportedly more energy efficient, and can execute significantly more instructions per cycle. Simultaneous multithreading, SMT has been introduced, allowing each core to run two thr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Secure Memory Encryption

Zen is the first iteration in the Zen family of computer processor microarchitectures from AMD. It was first used with their Ryzen series of CPUs in February 2017. The first Zen-based preview system was demonstrated at E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs, codenamed "Summit Ridge", reached the market in early March 2017, Zen-derived Epyc server processors launched in June 2017 and Zen-based APUs arrived in November 2017. Zen is a clean sheet design that differs from AMD's previous long-standing Bulldozer architecture. Zen-based processors use a 14 nm FinFET process, are reportedly more energy efficient, and can execute significantly more instructions per cycle. SMT has been introduced, allowing each core to run two threads. The cache system has also been redesigned, making the L1 cache write-back. Zen processors use three different sockets: desktop Ryzen chips use the AM4 socke ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Zen Microarchitecture

Zen is a family of computer processor microarchitectures from AMD, first launched in February 2017 with the first generation of Ryzen CPUs. It is used in Ryzen (desktop and mobile), Ryzen Threadripper (workstation and high-end desktop), and Epyc (server). Zen 5 is the latest iteration of the architecture. Comparison History First generation The first-generation Zen was launched with the Ryzen 1000 series of CPUs (codenamed Summit Ridge) in February 2017. The first Zen-based preview system was demonstrated at Electronic Entertainment Expo 2016, E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs reached the market in early March 2017, and Zen-derived Epyc server processors (codenamed "Naples") launched in June 2017 and Zen-based AMD Accelerated Processing Unit, APUs (codenamed "Raven Ridge") arrived in November 2017. This first iteration of Zen utilized GlobalFoundries' 14 nm manufac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Socket SP5

Socket SP5 (LGA 6096) is a zero insertion force land grid array CPU socket designed by AMD supporting its Zen 4-based Epyc server processors codenamed ''Genoa'' that launched on November 10, 2022. History In June 2017, with the launch of the first generation Epyc server processors, AMD introduced the SP3 socket. The SP3 socket covered three generations of Epyc processors, including Naples, Rome and Milan. AMD's Genoa processors contain up to 96 Zen 4 cores compared to Milan's maximum of 64 cores. In support of Genoa's 96 cores, AMD introduced the SP5 socket with 2022 more contact pins than the SP3 socket to provide greater power delivery and signal integrity. SP5 can provide a peak power of up to 700 W. The SP5 socket supports Epyc processors codenamed Bergamo, which have up to 128 small Zen 4c cores and were launched on June 13, 2023. Features * Supports 12 channels of DDR5 ECC RAM with 6 TB maximum capacity per socket. Using a dual socket system can allow up ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Socket SP6

Socket SP6 (LGA 4844) is a zero insertion force land grid array CPU socket designed by AMD supporting its Zen 4c-based ''Siena'' Epyc server processors that launched on September 18, 2023. It is designed for server systems targeting infrastructure and edge computing segments. History In November 2022, AMD launched the SP5 socket alongside its Epyc 9004 series of processors, codenamed Genoa. The large physical socket and thermal footprint excluded SP5 from certain edge applications. Socket SP6 was created as a smaller variant of socket SP5 with fewer pins and less memory support, reducing the footprint from 72×75.4 mm to 58.5×75.4 mm, identical to that of SP3. The SP6 platform comes in at a lower cost than the SP5 platform's Genoa and Bergamo server processors. Socket SP6 serves segments of the server market where performance is not a priority, but cost, value, small footprint, and low power consumption / heat dissipation are. Examples of this are infrastructure c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

AMD Epyc Wordmark

Advanced Micro Devices, Inc. (AMD) is an American multinational corporation and technology company headquartered in Santa Clara, California and maintains significant operations in Austin, Texas. AMD is a Information technology, hardware and Fabless manufacturing, fabless company that designs and develops List of AMD processors, central processing units (CPUs), List of AMD graphics processing units, graphics processing units (GPUs), field-programmable gate arrays (FPGAs), System on a chip, system-on-chip (SoC), and high-performance computing, high-performance computer solutions. AMD serves a wide range of business and consumer markets, including gaming, data centers, artificial intelligence (AI), and embedded systems. AMD's main products include List of AMD microprocessors, microprocessors, motherboard chipsets, embedded processors, and List of AMD graphics processing units, graphics processors for Server (computing), servers, workstations, personal computers, and embedded syst ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Socket SP3

Socket SP3 is a zero insertion force land grid array CPU socket designed by AMD supporting its Zen-, Zen 2- and Zen 3-based Epyc server processors, launched on June 20, 2017. Because the socket is physically the same size as socket TR4 and socket sTRX4, users can use CPU coolers not only designed for SP3, but also coolers designed for TR4 and sTRX4. Socket SP3 is a system in a package socket - that means most features required to make the system fully functional (such as memory, PCI Express, SATA controllers etc.) are fully integrated into the processor package, eliminating the need for a chipset to be placed on a motherboard. Variants for desktop platforms (as said below) are, eventually, requiring an additional chipset to unlock the functionality of the CPU. A processor using socket SP3 is mounted by inserting the CPU into a slide and fixing the slide assembly by tightening three screws using the torque wrenches normally provided alongside the motherboard. Automated processor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Socket AM5

Socket AM5 (LGA 1718) is a zero insertion force flip-chip land grid array (LGA) CPU socket designed by AMD that is used for AMD Ryzen microprocessors starting with the Zen 4 microarchitecture. AM5 was launched in September 2022 and is the successor to AM4. The Ryzen 7000 series processors were the first AM5 processors. The 7000 series added support for PCI Express 5.0 and DDR5. Background In March 2017, with the launch of its new Zen processors, AMD used the AM4 socket that they had previously used with their Bristol Ridge (derived from Excavator) powered Athlon X4 and some A-Series, a pin grid array (PGA) socket that they promised to support until 2020. Announcement At CES 2022, AMD CEO Lisa Su unveiled the AM5 socket and the integrated heat spreader design for the upcoming Ryzen 7000 processors due in late 2022. On May 23, 2022, AMD provided details about the AM5 socket, its corresponding motherboards, and Ryzen 7000 Series CPUs at Computex in Taipei, Taiwan. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

AMD64

x86-64 (also known as x64, x86_64, AMD64, and Intel 64) is a 64-bit extension of the x86 instruction set. It was announced in 1999 and first available in the AMD Opteron family in 2003. It introduces two new operating modes: 64-bit mode and compatibility mode, along with a new four-level paging mechanism. In 64-bit mode, x86-64 supports significantly larger amounts of virtual memory and physical memory compared to its 32-bit predecessors, allowing programs to utilize more memory for data storage. The architecture expands the number of general-purpose registers from 8 to 16, all fully general-purpose, and extends their width to 64 bits. Floating-point arithmetic is supported through mandatory SSE2 instructions in 64-bit mode. While the older x87 FPU and MMX registers are still available, they are generally superseded by a set of sixteen 128-bit vector registers (XMM registers). Each of these vector registers can store one or two double-precision floating-point numbers, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

GlobalFoundries

GlobalFoundries Inc. is a multinational semiconductor contract manufacturing and design company located in the Cayman Islands and headquartered in Malta, New York. Created by the divestiture of the manufacturing arm of AMD in March 2009, the company was privately owned by Mubadala Investment Company, a sovereign wealth fund of the United Arab Emirates, until an initial public offering (IPO) in October 2021. Mubadala remains the majority owner of the company with an 82% stake. The company manufactures integrated circuits on wafers designed for markets such as smart mobile devices, automotive, aerospace and defense, consumer internet of things (IoT) and for data centers and communications infrastructure. As of 2023, GlobalFoundries is the third-largest semiconductor foundry by revenue. It is the only one with operations in Singapore, the European Union, and the United States: one 200 mm and one 300 mm wafer fabrication plant in Singapore; one 300 mm plant in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

3 Nm Process

In semiconductor manufacturing, the 3 nm process is the next die shrink after the 5 nm MOSFET (metal–oxide–semiconductor field-effect transistor) technology node. South Korean chipmaker Samsung started shipping its 3 nm gate all around (GAA) process, named 3GAA, in mid-2022. On 29 December 2022, Taiwanese chip manufacturer TSMC announced that volume production using its 3 nm semiconductor node (N3) was underway with good yields. An enhanced 3 nm chip process called "N3E" may have started production in 2023. American manufacturer Intel planned to start 3 nm production in 2023. Samsung's 3 nm process is based on GAAFET (gate-all-around field-effect transistor) technology, a type of multi-gate MOSFET technology, while TSMC's 3 nm process still uses FinFET (fin field-effect transistor) technology, despite TSMC developing GAAFET transistors. Specifically, Samsung plans to use its own variant of GAAFET called MBCFET (multi-bridge channel fie ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

AMD-Vi

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU. In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-assisted virtualization capabilities while attaining reasonable performance. In 2005 and 2006, both Intel ( VT-x) and AMD (AMD-V) introduced limited hardware virtualization support that allowed simpler virtualization software but offered very few speed benefits. Greater hardware support, which allowed substantial speed improvements, came with later processor models. Software-based virtualization The following discussion focuses only on virtualization of the x86 architecture protected mode. In protected mode the operating system kernel runs at a higher privilege such as ring 0, and applications at a lower privilege such as ring 3. In software-based virtualization, a host OS has direct access to hardware while the guest OSs have limited a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |